ハードウェアアクセラレーション

ハードウェアアクセラレーションとは、ハードウェアアクセラレータと呼ばれるコンピュータハードウェアを用いて、汎用の中央処理装置(CPU)上で実行されるソフトウェアよりも高速に特定の機能を実行することです。CPU上で実行されるソフトウェアで計算可能なデータ変換は、適切なハードウェアアクセラレータ、あるいはその両方によっても計算可能です。

コンピューティングタスクをより効率的に実行するには、一般的に、ソフトウェアの改善、ハードウェアの改善、あるいはその両方に時間と費用を投資します。レイテンシの低減、スループットの向上、エネルギー消費の削減といった点で、長所と短所を持つ様々なアプローチがあります。

ソフトウェアに重点を置くことによる一般的な利点としては、汎用性の向上、開発の迅速化、非反復的なエンジニアリングコストの削減、移植性の向上、機能の更新やバグの修正 の容易さなどが挙げられますが、一般的な操作を計算するためのオーバーヘッドは発生します。

ハードウェアに重点を置くことの利点としては、スピードアップ、消費電力の削減、[ 1 ]レイテンシの低減、並列性の向上[ 2 ]および帯域幅の向上、集積回路上で利用可能な領域と機能コンポーネントの有効活用などが挙げられますが、その一方で、シリコン上にエッチングされた後の設計の更新能力の低下、機能検証のコスト増加、市場投入までの時間、部品の必要性の増加といったデメリットも抱えています。

汎用プロセッサから完全にカスタマイズされたハードウェアに至るまでのデジタルコンピューティングシステムの階層では、柔軟性と効率性の間にトレードオフがあり、特定のアプリケーションを階層の上位(つまり、よりカスタマイズされた側)に実装すると、効率性が桁違いに向上します。 [ 3 ]この階層には、CPUなどの汎用プロセッサ、[ 4 ] GPUのプログラマブルシェーダなどのより特殊なプロセッサ、[ 5 ]フィールドプログラマブルゲートアレイ(FPGA)上に実装されたアプリケーション、[ 6 ]特定用途向け集積回路(ASIC)上に実装された固定機能が含まれます。 [ 7 ]

ハードウェアアクセラレーションはパフォーマンスの面で有利であり、機能が固定されている場合に実用的であるため、ソフトウェアソリューションほど更新は必要ありません。FPGAなどの再プログラム可能なロジックデバイスの登場により、2010年以降、完全に固定されたアルゴリズムへのハードウェアアクセラレーションの制限が緩和され、アルゴリズムや処理制御フローの変更が必要な問題領域にハードウェアアクセラレーションを適用できるようになりました。[ 8 ] [ 9 ]ただし、多くのオープンソースプロジェクトでは、すべてのベンダーが配布または公開することに熱心ではない独自のライブラリが必要になるため、そのようなプロジェクトに統合するのが難しいという欠点があります。

概要

集積回路は、アナログ信号とデジタル信号の両方に対して様々な演算を処理できるように設計されています。コンピューティングにおいて、デジタル信号は最も一般的であり、通常は2進数で表現されます。コンピュータのハードウェアとソフトウェアは、この2進数表現を用いて演算を実行します。これは、2進数入力に対してブール関数を処理し、その結果を出力して保存したり、他のデバイスでさらに処理したりすることで行われます。

ハードウェアとソフトウェアの計算上の等価性

すべてのチューリングマシンはあらゆる計算可能な関数を実行できるため、特定のソフトウェアと同じ機能を実行するカスタムハードウェアを設計することは常に可能です。逆に、ソフトウェアは特定のハードウェアの機能をエミュレートするために常に使用できます。カスタムハードウェアは、ソフトウェアで指定できる同じ機能に対して、ワットあたりの性能がより高い場合があります。VerilogやVHDLなどのハードウェア記述言語(HDL)は、ソフトウェアと同じセマンティクスをモデル化し、その設計をFPGAにプログラムしたり、ASICの ロジックゲートに組み込んだりできるネットリストに合成できます。

プログラム内蔵型コンピュータ

ソフトウェアベースのコンピューティングの大部分は、フォン・ノイマン・アーキテクチャを実装したマシン上で行われ、これらは総称してプログラム格納型コンピュータと呼ばれます。コンピュータプログラムはデータとして格納され、プロセッサによって実行されます。このようなプロセッサは、ソフトウェアプログラムを構成する命令を実行するために、命令をフェッチしてデコードするだけでなく、メモリからデータオペランドをロードする必要があります(命令サイクルの一部として)。コードとデータの共通キャッシュに依存すると、「フォン・ノイマン・ボトルネック」が発生します。これは、フォン・ノイマン・アーキテクチャを実装したプロセッサ上のソフトウェアのスループットに根本的な制限をもたらします。命令とデータがメモリ階層内で別々のキャッシュを持つ修正ハーバード・アーキテクチャでさえ、命令オペコードのデコードと、マイクロプロセッサまたはマイクロコントローラ上で利用可能な実行ユニットの多重化にはオーバーヘッドがあり、回路利用率が低下します。同時マルチスレッド機能を提供する最新のプロセッサは、利用可能なプロセッサ機能ユニットの十分に活用されていない部分と、異なるハードウェアスレッド間の命令レベルの並列性を活用します。

ハードウェア実行ユニット

ハードウェア実行ユニットは、一般的にフォン・ノイマン型や修正ハーバード型アーキテクチャに依存せず、命令サイクルにおける命令フェッチとデコードの各ステップを実行する必要がなく、それらのステージのオーバーヘッドも発生しません。必要な計算がレジスタ転送レベル(RTL)のハードウェア設計で指定されている場合、命令フェッチとデコードの各ステージで発生する時間と回路面積のコストを回収し、他の用途に使用することができます。

この再利用により、計算時間、電力、回路面積が節約されます。再利用されたリソースは、並列計算、その他の機能、通信、メモリ、入出力機能の向上に使用できます。ただし、汎用性は犠牲になります。

新しいハードウェアアーキテクチャ

ハードウェア設計の RTL カスタマイズが進むと、インメモリ コンピューティング、トランスポート トリガー アーキテクチャ(TTA)、ネットワーク オン チップ(NoC) などの新しいアーキテクチャで、実行コンテキストに対するデータの局所性の向上によるメリットをさらに享受できるようになり、モジュールと機能ユニット間のコンピューティングと通信のレイテンシが削減されます。

カスタムハードウェアの並列処理能力は、集積回路ダイ上で利用可能な面積とロジックブロックによってのみ制限されます。[ 10 ]そのため、ハードウェアは汎用プロセッサ上のソフトウェアよりもはるかに自由に大規模な並列処理を提供でき、並列ランダムアクセスマシン(PRAM)モデルを実装する可能性を提供します。

マルチコアおよびメニーコア処理ユニットは、単一のFPGAまたはASIC上のマイクロプロセッサIPコア回路図から構築するのが一般的です。 [ 11 ] [ 12 ] [ 13 ] [ 14 ] [ 15 ]同様に、デジタル信号処理のように、特殊な機能ユニットはプロセッサIPコアに組み込むことなく並列に構成できます。そのため、特に大量のデータを扱う、条件分岐の少ない反復的で固定されたタスクには、ハードウェアアクセラレーションがしばしば用いられます。NvidiaのCUDAシリーズGPUは、このように実装されています 。

実装メトリクス

デバイスのモビリティが向上するにつれて、ハードウェアの物理的寸法、消費電力、演算スループットといった特性を考慮し、特定のアクセラレーションプロトコルの相対的な性能を測定する新しい指標が開発されてきました。これらは、タスク効率、実装効率、柔軟性という3つのカテゴリーにまとめることができます。適切な指標は、ハードウェアの面積に加え、対応する演算スループットと消費電力の両方を考慮します。[ 16 ]

アプリケーション

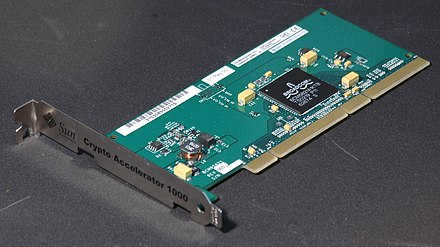

ハードウェアアクセラレーションの例としては、グラフィックス処理装置(GPU)のビットブリットアクセラレーション機能、ニューラルネットワークを加速するためのメモリスタの使用、正規表現サービス拒否(ReDoS)攻撃を防ぐことを目的としたサーバー業界におけるスパム制御のための正規表現ハードウェアアクセラレーションなどがあります。[ 17 ]アクセラレーションを実行するハードウェアは、汎用CPUの一部である場合もあれば、ハードウェアアクセラレータと呼ばれる独立したユニットである場合もありますが、通常は3Dアクセラレータや暗号化アクセラレータなどのより具体的な用語で呼ばれます。

従来、プロセッサはシーケンシャル(命令が1つずつ実行される)であり、命令フェッチによって制御される汎用アルゴリズム(例えば、一時的な結果をレジスタファイルとの間で移動すること)を実行するように設計されていました。ハードウェアアクセラレータは、より高い同時実行性を実現し、一時変数用の特定のデータパスを持ち、フェッチ・デコード・実行サイクルにおける命令制御のオーバーヘッドを削減することで、特定のアルゴリズムの実行を改善します。

現代のプロセッサはマルチコアで、多くの場合、並列処理の「単一命令複数データ」(SIMD)ユニットを備えています。このようなユニットはCPUに統合されている場合もあれば、 AMD AIエンジンなどの追加コンポーネントによって提供される場合もあります。[ 18 ]それでも、ハードウェアアクセラレーションは依然としてメリットをもたらします。ハードウェアアクセラレーションは、タスクやプログラム内で頻繁に実行される計算集約型のアルゴリズムに適しています。ハードウェアアクセラレーションは、粒度に応じて、小さな機能ユニットから大きな機能ブロック(MPEG-2の動き推定など)まで多岐にわたります。

アプリケーション別のハードウェアアクセラレーションユニット

| 応用 | ハードウェアアクセラレータ | 頭字語 |

|---|---|---|

| コンピュータグラフィックス | グラフィックス処理ユニット | グラフィックプロセッサ

|

| デジタル信号処理 | デジタル信号プロセッサ | DSP |

| アナログ信号処理 | フィールドプログラマブルアナログアレイ | FPAA

|

| 画像処理 | ウェブカメラまたは画像プロセッサ | IPU |

| サウンド処理 | サウンドカードとサウンドカードミキサー | 該当なし |

| コンピュータネットワーク | ネットワークプロセッサとネットワークインターフェースコントローラ | NPUとNIC

|

| 暗号化 | 暗号アクセラレータと安全な暗号プロセッサ | 該当なし |

| 人工知能 | AIアクセラレータ | 該当なし

|

| 多重線形代数 | テンソル処理ユニット | TPU |

| 物理シミュレーション | 物理演算処理装置 | PPU |

| 正規表現[ 17 ] | 正規表現コプロセッサ | 該当なし |

| データ圧縮[ 20 ] | データ圧縮アクセラレータ | 該当なし |

| インメモリ処理 | ネットワークオンチップとシストリックアレイ | NoC; 該当なし |

| データ処理 | データ処理ユニット | DPU |

| あらゆるコンピューティングタスク | コンピューターハードウェア

| 宿題(時々)

|

参照

- コプロセッサ

- DirectX ビデオ アクセラレーション(DXVA)

- ダイレクトメモリアクセス(DMA)

- 高位合成

- ソフトマイクロプロセッサ

- フリンによる並列コンピュータアーキテクチャの分類

- 単一命令複数データ(SIMD)

- 単一命令複数スレッド(SIMT)

- 複数命令、複数データ(MIMD)

- 機能を備えた操作用コンピュータ

参考文献

- ^ 「マイクロソフト、プログラム可能なチップでBing検索を強化」 WIRED 、 2014年6月16日。

- ^ 「Embedded」 . 2007年10月8日時点のオリジナルよりアーカイブ。2012年8月18日閲覧。「FPGAアーキテクチャ AからZまで」クライブ・マックスフィールド著 2006

- ^ Sinan, Kufeoglu; Mahmut, Ozkuran (2019). 「図5. 難易度再計算間のCPU、GPU、FPGA、ASICの最小エネルギー消費量」.ビットコインマイニングのエネルギー消費量. doi : 10.17863/CAM.41230 .

- ^ Kim, Yeongmin; Kong, Joonho; Munir, Arslan (2020). 「エッジでのCNNアクセラレーションのためのCPUアクセラレータ協調スケジューリング」 . IEEE Access . 8 : 211422– 211433. Bibcode : 2020IEEEA...8u1422K . doi : 10.1109/ACCESS.2020.3039278 . ISSN 2169-3536 .

- ^ Lin, Yibo; Jiang, Zixuan; Gu, Jiaqi; Li, Wuxi; Dhar, Shounak; Ren, Haoxing; Khailany, Brucek; Pan, David Z. (2021年4月). 「DREAMPlace: ディープラーニングツールキットを活用した最新のVLSI配置のためのGPUアクセラレーション」. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems . 40 (4): 748– 761. Bibcode : 2021ITCAD..40..748L . doi : 10.1109/TCAD.2020.3003843 . ISSN 1937-4151 . S2CID 225744481 .

- ^ Lyakhov, Pavel; Valueva, Maria; Valuev, Georgii; Nagornov, Nikolai (2020-12-18). 「切り捨てられた乗算累算ユニットに基づくデジタルフィルタ性能向上手法」 .応用科学. 10 (24): 9052. doi : 10.3390/app10249052 . ISSN 2076-3417 .

FPGAによるハードウェアシミュレーションにより、デジタルフィルタ性能が向上しました。

- ^ Mohan, Prashanth; Wang, Wen; Jungk, Bernhard; Niederhagen, Ruben; Szefer, Jakub; Mai, Ken (2020年10月). 「ポスト量子デジタル署名方式XMSS向け28nm ASICアクセラレータ」. 2020 IEEE 38th International Conference on Computer Design (ICCD) . ハートフォード, コネチカット州, 米国: IEEE. pp. 656– 662. doi : 10.1109/ICCD50377.2020.00112 . ISBN 978-1-7281-9710-4. S2CID 229330964 .

- ^ Morgan, Timothy Pricket (2014年9月3日). 「MicrosoftがFPGAを活用してBing検索を高速化する方法」 . Enterprise Tech . 2018年9月18日閲覧。

- ^ 「Project Catapult」。Microsoft Research。

- ^ MicroBlaze ソフトプロセッサ: よくある質問アーカイブ2011-10-27 at the Wayback Machine

- ^ Vassányi, István (1998). 「FPGAにおけるプロセッサアレイの実装」 .フィールドプログラマブルロジックとFPGAからコンピューティングパラダイムへの応用. コンピュータサイエンス講義ノート. 第1482巻. pp. 446– 450. doi : 10.1007/BFb0055278 . ISBN 978-3-540-64948-9。

- ^ Zhoukun WANGとOmar HAMMAMI. 「ネットワークオンチップを備えた24プロセッサシステムオンチップFPGA設計」. [1]

- ^ 「ジョン・ケント。『Micro16アレイ - シンプルなCPUアレイ』」. 2020年8月1日時点のオリジナルよりアーカイブ。2018年10月7日閲覧。

- ^キット・イートン「1,000コアCPUの実現:将来のデスクトップはスーパーコンピュータになる」2011年[2]

- ^「科学者らが1,000個以上のコアを1つのチップに詰め込む」2011年。 [3] 2012年3月5日アーカイブ、 Wayback Machine

- ^ Kienle, Frank; Wehn, Norbert; Meyr, Heinrich (2011年12月). 「チャネルデコーダの複雑性、エネルギー効率、実装効率について」. IEEE Transactions on Communications . 59 (12): 3301– 3310. arXiv : 1003.3792 . Bibcode : 2011ITCom..59.3301K . doi : 10.1109/tcomm.2011.092011.100157 . ISSN 0090-6778 . S2CID 13863870 .

- ^ a b「ハードウェアにおける正規表現」 。 2014年7月17日閲覧。

- ^ Rico, Alejandro; Pareek, Satyaprakash; Cabezas, Javier; Clarke, David; Ozgul, Baris; Barat, Francisco; Fu, Yao; Münz, Stephan; Stuart, Dylan; Schlangen, Patrick; Duarte, Pedro; Date, Sneha; Paul, Indrani; Weng, Jian; Santan, Sonal (2024-07-10). "Ryzen AIプロセッサにおけるAMD XDNA NPU". IEEE Micro . 44 (6): 73– 82. Bibcode : 2024IMicr..44f..73R . doi : 10.1109/MM.2024.3423692 . ISSN 1937-4143 .

- ^ 「Intel® PRO/100 S デスクトップ アダプタ データシート」(PDF) . Intel . 2005 . 2025年8月15日閲覧。

- ^ 「圧縮アクセラレータ」。Microsoft Research。2014年6月16日。 2025年8月15日閲覧。

- ^ a b Farabet, Clément; et al. (2010).合成視覚システム向けハードウェア加速畳み込みニューラルネットワーク. Proceedings of 2010 IEEE International Symposium on Circuits and Systems. Paris: IEEE . pp. 257– 260. doi : 10.1109/ISCAS.2010.5537908 . ISSN 2158-1525 . 2025年8月15日閲覧– Academia.edu経由。

外部リンク

ウィキメディア・コモンズのハードウェアアクセラレーション関連メディア

ウィキメディア・コモンズのハードウェアアクセラレーション関連メディア