PMOSロジック

PMOSまたはpMOSロジックは、pチャネル金属酸化膜半導体(P-Channel Metal-Oxide-Semiconductor)の略で、pチャネルのエンハンスメントモード金属酸化膜半導体電界効果トランジスタ(MOSFET)をベースにしたデジタル回路の一種です。1960年代後半から1970年代初頭にかけて、PMOSロジックは大規模集積回路(LSI)の主流の半導体技術でしたが、その後NMOSおよびCMOSデバイスに取って代わられました。

歴史と応用

1959年、モハメド・アタラとダウォン・カーンはベル研究所で最初の実用的なMOSFETを製造しました。[ 1 ]彼らはPMOSとNMOSの両方のデバイスを製造しましたが、実際に動作したのはPMOSデバイスだけでした。[ 2 ]製造プロセスにおける汚染物質(特にナトリウム)が適切に管理され、実用的なNMOSデバイスを製造できるようになるまでには10年以上かかりました。

当時集積回路に使用できる唯一のデバイスであったバイポーラ接合トランジスタと比較すると、 MOSFET には次のような多くの利点があります。

- 同様の精度の半導体デバイス製造プロセスを考えると、MOSFETはバイポーラ接合トランジスタの面積のわずか10%しか必要としません。[ 3 ]:87 主な理由は、MOSFETが自己絶縁性であり、チップ上の隣接するコンポーネントからのp-n接合分離を必要としないことです。

- MOSFETはプロセスステップ数が少なく、製造が簡単で安価です(拡散ドーピングステップは1つ[ 3 ] : 87 です が、バイポーラプロセスでは4つ[ 3 ] : 50 です )。

- MOSFET には静的ゲート電流がないので、MOSFET をベースにした集積回路の消費電力は低くなります。

バイポーラ集積回路と比較した欠点は次のとおりです。

ゼネラル・マイクロエレクトロニクス社は1964年に最初の商用PMOS回路、120個のMOSFETを搭載した20ビットのシフトレジスタを発表しました。これは当時としては信じられないレベルの集積度でした。[ 5 ]ゼネラル・マイクロエレクトロニクス社が1965年にビクター・コンプトメーター社向けのビクター3900電子計算機用に23個のカスタム集積回路を開発しようとした試み[ 5 ]は、当時のPMOS回路の信頼性を考えるとあまりにも野心的であることが判明し、最終的にゼネラル・マイクロエレクトロニクス社の消滅につながりました。[ 6 ]他の企業は、当時のバイポーラ技術では実現不可能だった 大型シフトレジスタ(ゼネラル・インスツルメンツ社)[ 7 ]やアナログマルチプレクサ3705(フェアチャイルドセミコンダクター社)[ 8 ]などのPMOS回路を製造し続けました。

1968 年にポリシリコン自己整合ゲート技術が導入されて大きな改善がもたらされました。[ 9 ]フェアチャイルド セミコンダクターのTom Klein とFederico Faggin は、自己整合ゲート プロセスを改良して商業的に実現可能にし、最初のシリコン ゲート集積回路であるアナログ マルチプレクサ 3708 をリリースしました。[ 9 ]自己整合ゲート プロセスにより、製造公差が狭くなり、MOSFET が小型化されるとともに、ゲート容量が低減して一定になりました。たとえば、PMOS メモリの場合、この技術によりチップ面積は半分で 3 ~ 5 倍の速度が実現されました。[ 9 ]ポリシリコン ゲート材料により、自己整合ゲートが可能になっただけでなく、しきい値電圧が低下し、その結果、最小電源電圧が低くなり (たとえば、-16 V [ 10 ] : 1–13 )、消費電力が削減されました。シリコンゲートPMOSロジックは電源電圧が低いため、高電圧PMOSと呼ばれていた古いメタルゲートPMOSとは対照的に、低電圧PMOSと呼ばれることが多い。[ 3 ]:89

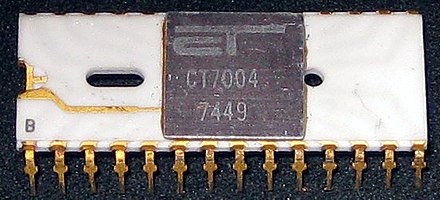

さまざまな理由から、フェアチャイルドセミコンダクターは、関係する経営陣が望んだほど集中的に PMOS 集積回路の開発を進めなかった。[ 11 ] : 1302 そのうちの 2 人、ゴードン・ムーアとロバート・ノイスは、1968 年に独自の新興企業であるインテルを設立することを決定した。その後まもなく、フェデリコ・ファギンやレス・ヴァダスなど、他のフェアチャイルドのエンジニアも加わった。インテルは1969 年に、容量 256 ビットの初の PMOSスタティック RAMである Intel 1101 を発表した。 [ 11 ] : 1303 1970 年には、1024 ビットのダイナミック RAM であるIntel 1103が続いた。 [ 12 ] 1103 は商業的に成功し、すぐにコンピューターの磁気コアメモリーに取って代わり始めた。[ 12 ]インテルは1971年に初のPMOSマイクロプロセッサであるインテル4004を発表しました。多くの企業がインテルに続きました。初期のマイクロプロセッサのほとんどはPMOS技術で製造されていました。インテルからは4040と8008 、ナショナル セミコンダクターからはIMP-16、PACE、SC/MP、テキサスインスツルメンツからはTMS1000、ロックウェル インターナショナルからはPPS-4 [ 13 ]とPPS-8 [ 14 ]が製造されました。このマイクロプロセッサのリストには、初の商用マイクロプロセッサが含まれています。初の4ビット マイクロプロセッサ (4004)、初の8ビット マイクロプロセッサ (8008)、初のシングルチップ16ビット マイクロプロセッサ (PACE)、初のシングルチップ4ビット マイクロコントローラ (TMS1000; CPUと同じチップ上にRAMとROMが搭載)

1972年までに、NMOS技術は、ついに商用製品に使用できるレベルにまで開発されました。Intel (2102) [ 15 ]とIBM [ 12 ]はともに、1kビットのメモリチップを発表しました。NMOS MOSFETのn型チャネルの電子移動度は、PMOS MOSFETのp型チャネルのホール移動度の約3倍であるため、NMOSロジックはスイッチング速度の向上を可能にします。このため、NMOSロジックはすぐにPMOSロジックに取って代わり始めました。1970年代後半までには、NMOSマイクロプロセッサがPMOSプロセッサを追い越しました。[ 16 ] PMOSロジックは、コストが低く、単純な計算機や時計などのアプリケーションでの比較的高いレベルの統合が可能であったため、しばらく使用され続けました。CMOS技術は、PMOSやNMOSよりも大幅に低い消費電力を約束しました。 CMOS回路は1963年にフランク・ワンラス[ 17 ]によって既に提案され、RCA社は1968年に4000シリーズCMOS集積回路の商用生産を開始していたにもかかわらず、CMOSは製造が複雑であり、PMOSやNMOSほどの集積度もNMOSほどの速度も得られませんでした。CMOSがマイクロプロセッサの主要技術としてNMOSに取って代わるまでには、1980年代までかかりました。

説明

PMOS回路は、 NMOSやCMOS回路と比較して、複数の異なる電源電圧(正負両方)が必要であること、導通状態での消費電力が大きいこと、比較的大きな面積を必要とすることなど、多くの欠点があります。また、全体的なスイッチング速度も低くなります。

PMOSは、pチャネル(+)金属酸化膜半導体電界効果トランジスタ(MOSFET)を用いて、論理ゲートやその他のデジタル回路を実装します。PMOSトランジスタは、 n型トランジスタのボディに反転層を形成することで動作します。このpチャネルと呼ばれる反転層は、p型の「ソース」端子と「ドレイン」端子の間でホールを伝導します。

pチャネルは、ゲートと呼ばれる3番目の端子に負電圧(-25Vが一般的でした[ 18 ])を印加することで生成されます。他のMOSFETと同様に、PMOSトランジスタには、カットオフ(またはサブスレッショルド)、トライオード、飽和(アクティブと呼ばれることもあります)、および速度飽和の4つの動作モードがあります。

PMOSロジックは設計と製造が容易(MOSFETを抵抗として動作させることができるため、回路全体をPMOS FETで構成可能)ですが、いくつかの欠点も存在します。最大の問題は、いわゆる「プルアップネットワーク」(PUN)がアクティブなとき、つまり出力がハイのとき、PMOSロジックゲートに直流電流(DC)が流れることです。そのため、回路がアイドル状態のときでも静的な電力消費が発生します。

また、PMOS回路はハイからローへの遷移が遅いです。ローからハイへの遷移時、トランジスタは低い抵抗値を提供するため、出力の容量性電荷は非常に速く蓄積されます(非常に低い抵抗値を介してコンデンサを充電する場合と同様)。しかし、出力と負電源レール間の抵抗値ははるかに大きいため、ハイからローへの遷移にはより長い時間がかかります(高い抵抗値を介してコンデンサを放電する場合と同様)。抵抗値の低いものを使用すると、このプロセスは高速化されますが、静的消費電力も増加します。

さらに、非対称の入力ロジックレベルにより、PMOS回路はノイズの影響を受けやすくなります。[ 19 ]

ほとんどのPMOS集積回路は17~24ボルトのDC電源を必要とする。[ 20 ]しかし、 Intel 4004 PMOSマイクロプロセッサは、金属ゲートではなくポリシリコンを用いたPMOSロジックを採用しており、電圧差を小さく抑えている。TTL信号との互換性を確保するため、4004は正電源電圧V SS =+5V、負電源電圧V DD = -10Vを使用している。[ 21 ]

ゲイツ

p型MOSFETは、ロジックゲート出力と正電源電圧の間にいわゆる「プルアップネットワーク」(PUN)として配置され、ロジックゲート出力と負電源電圧の間には抵抗が配置されています。この回路は、目的の出力がハイレベルの場合、PUNがアクティブになり、正電源と出力の間に電流経路が形成されるように設計されています。

PMOSゲートは、すべての電圧を逆にした場合、NMOSゲートと同じ配置になります。[ 22 ] したがって、アクティブハイロジックの場合、ド・モルガンの法則によれば、PMOS NORゲートはNMOS NANDゲートと同じ構造を持ち、その逆も同様です。

|  |  |

参考文献

- ^ 「1960年:金属酸化膜半導体(MOS)トランジスタの実証」コンピュータ歴史博物館。

- ^ Lojek, Bo (2007).半導体工学の歴史. Springer Science & Business Media . pp. 321–323 . ISBN 9783540342588。

- ^ a b c dマンフレッド・セイファート (1982)。Digitale Schaltungen und Schaltkreise [デジタル回路と集積回路] (ドイツ語)。ベルリン: VEB Verlag Technik。OCLC 923116729。

- ^ Mogisters: 新世代MOSモノリシックシフトレジスタ。General Instrument Corp. 1965年。

- ^ a b「1964年:初の商用MOS ICの導入」。コンピュータ歴史博物館。 2020年12月7日閲覧。

- ^ 「13 Sextillion & Counting: The Long and Winding Road to the Most frequently Manufactured Human Artifact in History」コンピュータ歴史博物館. 2018年4月2日. 2020年12月8日閲覧。

- ^汎用計測機器用MOS集積回路。汎用計測機器マイクロエレクトロニクス部門。1966年9月。

- ^ MJ Robles (1968-04-09).新しいMOSマルチプレックススイッチはバイポーラ互換です。フェアチャイルドセミコンダクター。

- ^ a b c「1968年:IC向けシリコンゲート技術の開発」コンピュータ歴史博物館. 2020年12月11日閲覧。

- ^ Intelメモリ設計ハンドブック(PDF) . Intel. 1973年8月. 2020年10月5日時点のオリジナルよりアーカイブ。 2020年12月18日閲覧。

- ^ a b Sah, Chih-Tang (1988年10月). 「MOSトランジスタの進化:構想からVLSIまで」(PDF) . Proceedings of the IEEE . 76 (10): 1280– 1326. doi : 10.1109/5.16328 . ISSN 0018-9219 .

- ^ a b c「1970年:MOSダイナミックRAMが磁気コアメモリと価格で競合」コンピュータ歴史博物館. 2020年12月17日閲覧。

- ^ 「Rockwell PPS-4」 . The Antique Chip Collector's Page . 2020年12月21日閲覧。

- ^並列処理システム(PPS)マイクロコンピュータ。ロックウェル・インターナショナル。1974年10月。 2020年12月21日閲覧。

- ^ 「インテル製品の時系列リスト。製品は日付順に並べられています」(PDF)。インテルミュージアム。インテルコーポレーション。2005年7月。2007年8月9日時点のオリジナル(PDF)からアーカイブ。 2007年7月31日閲覧。

- ^ Kuhn, Kelin (2018). 「CMOSとCMOSの先へ:スケーリングの課題」. CMOSアプリケーション向け高移動度材料. Woodhead Publishing . p. 1. ISBN 9780081020623。

- ^ 「1963年:相補型MOS回路構成が発明される」コンピュータ歴史博物館. 2021年1月2日閲覧。

- ^ Ken Shirriff (2020年12月). 「4相ロジックを搭載した初期の計算機チップのリバースエンジニアリング」 . 2020年12月31日閲覧。

- ^カーン、アフマド・シャヒド(2014年)『マイクロ波工学:概念と基礎』CRCプレス、629頁。ISBN 97814665914242016年4月10日閲覧。

また、非対称の入力ロジックレベルにより、PMOS回路はノイズの影響を受けやすくなります。

- ^ Fairchild (1983年1月). 「CMOS、理想的なロジックファミリー」(PDF) . p. 6. 2015年1月9日時点のオリジナル(PDF)からアーカイブ。 2015年7月3日閲覧。

一般的なP-MOS部品のほとんどは17V~24Vの電源電圧で規定されていますが、CMOSの最大電源電圧は15Vです。

- ^ 「Intel 4004 データシート」(PDF) (2010年7月6日公開). 1987年. p. 7. 2016年10月16日時点のオリジナル(PDF)からのアーカイブ。 2011年7月6日閲覧。

- ^マイクロエレクトロニクスデバイスデータハンドブック(PDF) (NPC 275-1版). NASA / ARINC Research Corporation. 1966年8月. pp. 2– 51.

さらに読む

- Savard, John JG (2018) [2005]. 「コンピューターの構成要素」 . quadibloc . 2018年7月2日時点のオリジナルよりアーカイブ。 2018年7月16日閲覧。