スーパースカラプロセッサ

|

スーパースカラプロセッサ(またはマルチ発行プロセッサ[ 1 ])は、命令レベルの並列処理と呼ばれる形式の並列処理を単一のプロセッサ内で実装するCPUです。 [ 2 ]クロックサイクルごとに最大で 1 つの命令しか実行できないスカラプロセッサとは対照的に、スーパースカラプロセッサは、プロセッサ上の異なる実行ユニットに複数の命令を同時にディスパッチすることにより、クロックサイクル中に複数の命令を実行したり、実行を開始したりできます。そのため、特定のクロックレートで可能な場合よりも高いスループット(単位時間あたりに実行できる命令の数。1 未満になる場合もあります)が可能になります。各実行ユニットは、独立したプロセッサ(プロセッサがマルチコアプロセッサの場合はコア)ではなく、算術論理ユニットなどの単一の CPU 内の実行リソースです。

スーパースカラCPUも通常はパイプライン化されていますが、スーパースカラとパイプライン実行は異なるパフォーマンス向上手法と考えられています。前者(スーパースカラ)は複数の実行ユニットを用いて複数の命令を並列に実行しますが、後者(パイプライン)は実行ユニットを異なるフェーズに分割することで、同じ実行ユニット内で複数の命令を並列に実行します。「単純なスーパースカラパイプライン」の図では、2つの命令を同時にフェッチすることがスーパースケーリングであり、最初の命令ペアが書き戻される前に次の2つの命令をフェッチすることがパイプラインです。

スーパースカラー技術は、伝統的に、いくつかの識別特性(特定の CPU 内)と関連付けられています。

- 命令は順次命令ストリームから発行される

- CPUは実行時に命令間のデータ依存性を動的にチェックします(コンパイル時のソフトウェアチェックとは対照的)

- CPUはクロックサイクルごとに複数の命令を実行できる

歴史

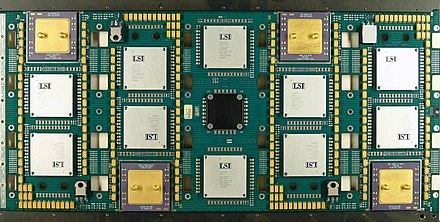

1964年のシーモア・クレイのCDC 6600は、1サイクルあたり複数の命令を発行することはできないものの、複数の機能ユニットで同時に命令を実行する能力があるため、現代のスーパースカラ・プロセッサに影響を与えた初期製品としてしばしば挙げられる。1967年のIBM System/360 Model 91も、アウトオブオーダー実行を導入し、トマスロのアルゴリズムの先駆的な使用法を示した初期製品である。[ 3 ] Intel i960 CA(1989年)、[ 4 ] AMD 29000シリーズ29050(1990年)、およびモトローラMC88110(1991年)[ 5 ]マイクロプロセッサは、最初の商用シングルチップ・スーパースカラ・マイクロプロセッサであった。このようなRISCマイクロプロセッサは、スーパースカラー実行を採用した最初のプロセッサです。RISC アーキテクチャでは、トランジスタとダイ領域が解放されるため、複数の実行ユニットを組み込むことができ、また、命令セットの従来の統一性によりスーパースカラー ディスパッチが容易になるためです (このため、1980 年代から 1990 年代にかけて、RISC 設計はCISC設計よりも高速でした。また、命令のビット長が可変の場合、複数のディスパッチを実行するのははるかに複雑です)。

低電力アプリケーション、組み込みシステム、バッテリ駆動デバイスで使用される CPU を除き、1998 年頃から開発された汎用 CPU は基本的にすべてスーパースカラーです。

P5 Pentiumは初のスーパースカラー x86 プロセッサでした。Nx586 、P6 Pentium Pro、AMD K5は、スーパースカラーマイクロアーキテクチャで実際に実行する前に、x86命令を非同期的に動的なマイクロコードのようなマイクロオペレーション シーケンスにデコードする最初の設計の 1 つです。これにより、バッファリングされた部分的な命令の動的スケジュールが可能になり、より単純な P5 Pentium で使用されていたより厳格な方法に比べて、より多くの並列処理を引き出すことができました。また、投機的実行が簡素化され、高度なCyrix 6x86などの設計に比べて高いクロック周波数を実現できました。

スカラーからスーパースカラーへ

最も単純なプロセッサはスカラープロセッサです。スカラープロセッサで実行される各命令は、通常、一度に1つまたは2つのデータ項目を操作します。一方、ベクトルプロセッサで実行される各命令は、多数のデータ項目を同時に処理します。これは、スカラー演算とベクトル演算の違いに似ています。スーパースカラープロセッサは、これら2つの要素を組み合わせたものです。各命令は1つのデータ項目を処理しますが、各CPU内に複数の実行ユニットが存在するため、複数の命令が別々のデータ項目を同時に処理できます。

スーパースカラCPUの設計では、命令ディスパッチャの精度向上と、複数の実行ユニットを常に使用可能にすることに重点を置いています。これは、ユニット数が増加するにつれてますます重要になっています。初期のスーパースカラCPUは2つのALUと1つのFPUを搭載していましたが、 PowerPC 970などの後期の設計では、4つのALU、2つのFPU、そして2つのSIMDユニットが搭載されています。ディスパッチャがこれらのユニットすべてに命令を供給し続けることができなければ、システムのパフォーマンスは、よりシンプルで安価な設計と変わりません。

スーパースカラプロセッサは通常、マシンサイクルあたり1命令を超える実行速度を維持します。しかし、複数の命令を同時に処理するだけでは、アーキテクチャがスーパースカラになるわけではありません。パイプライン、マルチプロセッサ、またはマルチコアアーキテクチャでも、異なる方法で同様の処理が実現されるためです。

スーパースカラCPUでは、ディスパッチャがメモリから命令を読み取り、並列実行可能な命令を決定し、各命令を単一のCPU内に含まれる複数の実行ユニットのいずれかにディスパッチします。したがって、スーパースカラプロセッサは複数の並列パイプラインを備え、各パイプラインが単一の命令スレッドからの命令を同時に処理していると考えることができます。

最新のスーパースカラー CPU のほとんどには、パイプラインの停止を回避し、並列実行を向上させるために命令を並べ替えるロジックも備わっています。

制限事項

スーパースカラー技術によるパフォーマンスの向上は、次の 3 つの主要な領域によって制限されます。

- 命令ストリーム内の固有の並列度(CPUから同じ計算リソースを必要とする命令)

- 依存性チェックロジックとレジスタ名変更回路の複雑さと時間コスト

- 分岐命令処理

既存のバイナリ実行可能プログラムは、様々なレベルの固有の並列性を備えています。命令が互いに依存せず、同時に実行できる場合もあります。また、命令同士が相互に依存し、一方の命令が他方の命令のリソースまたは結果に影響を与える場合もあります。a = b + c; d = e + fこれらの命令は、結果が他の計算に依存しないため、並列実行が可能です。ただし、a = b + c; b = e + f命令がユニット間を移動する際の完了順序によっては、並列実行できない場合もあります。

命令ストリームに命令間の依存関係が含まれていない場合でも、スーパースカラー CPU はその可能性をチェックする必要があります。そうでない場合の保証はなく、依存関係を検出できないと誤った結果が生成されるためです。

半導体プロセスがどれほど進歩し、スイッチング速度がどれほど高速であっても、同時にディスパッチできる命令数には実質的な限界があります。プロセスの進歩により、より多くの実行ユニット(例えばALU)が使用可能になりますが、命令の依存関係をチェックする負担は急速に増大し、依存関係を軽減するためのレジスタリネーミング回路の複雑さも増大します。消費電力、複雑さ、ゲート遅延コストのすべてが、スーパースカラの実現可能な高速化を制限します。

しかし、従来のスーパースカラCPUに非常に高速な依存性チェックロジックを備えていても、命令ストリーム自体に多くの依存性がある場合、高速化の可能性は制限されます。つまり、コードストリームの固有の並列度が、第二の制限となります。

代替案

これらの制限により、 VLIW (超長命令語)、 EPIC (明示的並列命令コンピューティング)、SMT (同時マルチスレッド)、マルチコア コンピューティングなどの代替アーキテクチャの変更の調査が促進されます。

VLIWでは、実行時にハードウェアロジックによる依存関係チェックという煩雑なタスクがなくなり、コンパイラに委譲されます。明示的並列命令コンピューティング(EPIC)は、VLIWにキャッシュプリフェッチ命令を追加したようなアーキテクチャです。

同時マルチスレッド(SMT)は、スーパースカラプロセッサの全体的な効率を向上させる技術です。SMTは、複数の独立した実行スレッドを許可することで、最新のプロセッサアーキテクチャが提供するリソースをより有効に活用することを可能にします。スレッドが独立しているということは、あるスレッドの命令を別のスレッドの命令とアウトオブオーダーで実行したり、並列に実行したりできることを意味します。また、ある独立したスレッドが、分岐などによって別のスレッドのコードストリームにパイプラインバブルを発生させることもありません。

スーパースカラプロセッサは、複数の実行ユニットがプロセッサ全体ではないという点で、マルチコアプロセッサとは異なります。単一のプロセッサは、 ALU、整数乗算器、整数シフタ、FPUなどのより細分化された実行ユニットで構成されています。各実行ユニットには複数のバージョンが存在する場合があり、これにより、多数の命令を並列に実行できます。これは、処理ユニット(「コア」と呼ばれる)ごとに1つのスレッドが複数のスレッドからの命令を同時に処理するマルチコアプロセッサとは異なります。また、パイプラインプロセッサとも異なります。パイプラインプロセッサでは、複数の命令がアセンブリラインのように、同時に様々な実行段階にあります。

様々な代替手法は相互に排他的ではなく、単一のプロセッサ内で組み合わせることが可能です(そして多くの場合、組み合わせて使用されています)。したがって、各コアが独立したプロセッサであり、複数の並列パイプライン(各パイプラインはスーパースカラ)を備えたマルチコアCPUが実現可能です。一部のプロセッサにはベクトル機能も搭載されています。

参照

- 熱心な実行

- ハイパースレッディング

- 同時マルチスレッド

- アウトオブオーダー実行

- 棚バッファ

- 投機的実行

- ソフトウェア ロックアウト、スーパースカラーのロジック依存性に似たマルチプロセッサの問題

- スーパースレッディング

参考文献

- ^ P. Pacheco、『並列プログラミング入門』、2011年、セクション2.2.5、「ILPには、パイプライン処理とマルチ発行という2つの主なアプローチがあります。動的マルチ発行をサポートするプロセッサは、スーパースカラーと呼ばれることもあります。」 A. Chien、『科学者のためのコンピュータアーキテクチャ』、2022年、102ページ、「マルチ発行(別名スーパースカラー)」。

- ^ 「スーパースカラープロセッサとは? - Techopediaによる定義」Techopedia.com、2019年2月28日。 2022年8月29日閲覧。

- ^スミス、ジェームス E.ソヒ、グリンダー S. (1995 年 12 月)。「スーパースカラー プロセッサのマイクロアーキテクチャ」(PDF)。IEEE の議事録。83 (12): 1609。ビブコード: 1995IEEEP..83.1609S。土井:10.1109/5.476078。

- ^ McGeady, Steven (1990年春). 80960アーキテクチャのi960CA SuperScalar実装. 第35回IEEEコンピュータソサエティ国際知的レバレッジ会議. pp. 232– 240. doi : 10.1109/CMPCON.1990.63681 . ISBN 0-8186-2028-5. S2CID 13206773 .

- ^ Diefendorff, K.; Allen, M. (1992年春). 「モトローラ88110スーパースカラRISCマイクロプロセッサ」. COMPCON 1992年春号論文集. pp. 157– 162. doi : 10.1109/CMPCON.1992.186702 . ISBN 0-8186-2655-0. S2CID 34913907 .

- マイク・ジョンソン著『スーパースカラ・マイクロプロセッサ設計』、Prentice-Hall、1991年、ISBN 0-13-875634-1

- ソリン・コトファナ、スタマティス・ヴァシリアディス、「スーパースカラーマシンの発行ロジックの設計複雑性について」、EUROMICRO 1998: 10277-10284

- Steven McGeady他「スーパースカラ i960MM 組み込みマイクロプロセッサのパフォーマンス強化」、ACM Proceedings of the 1991 Conference on Computer Architecture (Compcon)、1991 年、4 ~ 7 ページ

外部リンク

- 積極的な実行 / デュアルパス / マルチパス、マーク・スマザーマン著