PCIエクスプレス

| 周辺機器相互接続エクスプレス | |

| |

| 作成年 | 2003 (2003年) |

|---|---|

| 作成者 | |

| 取って代わる | |

| ビット幅 | 1レーンあたり1台、最大16レーン[ 1 ] |

| デバイス数 | 各接続の各エンドポイントに1つずつ[ a ] |

| スピード | デュアルシンプレックス、最大 242 GB/秒 |

| スタイル | シリアル |

| ホットプラグインターフェース | オプション(ExpressCard、OCuLink、CFexpress、U.2でサポート) |

| 外部インターフェース | オプション(OCuLinkまたは他の形式のPCI Express 外部ケーブルでサポートされ、USB4およびThunderbolt経由でトンネリングされます) |

| Webサイト | pcisig.com |

- PCI Express ×4

- PCI Express ×16

- PCI Express ×1

- PCI Express ×16

- 従来のPCI(32ビット、5V)

PCI Express(Peripheral Component Interconnect Express)は、正式名称をPCIe [ 2 ]と略し、コンピュータ内部のハードウェアコンポーネントを接続するために使用される高速規格です。PCI 、PCI-X、AGPなどの従来の拡張バス規格を置き換えるために設計されています。PCI -SIG (PCI Special Interest Group)によって開発および保守されているPCIeは、グラフィックカード、サウンドカード、Wi-Fiおよびイーサネットアダプタ、そしてソリッドステートドライブやハードディスクドライブなどのストレージデバイスの接続に広く使用されています。[ 3 ]

PCIeは、従来の規格と比較して、データ転送速度が速く、使用するピン数が少なく、占有スペースが小さく、コンピューターの動作中でもデバイスの追加や取り外し(ホットスワップ)が可能です。また、エラー検出機能が向上し、高度なコンピューティングニーズに対応するI/O仮想化などの新機能もサポートしています。[ 4 ]

PCIe接続は、データを送受信する導体のペアであるレーンを介して行われます。デバイスは、転送する必要があるデータ量に応じて、1つまたは複数のレーンを使用できます。 [ 5 ] PCIeテクノロジーは、ラップトップの拡張カード(ExpressCardなど)や、 M.2、U.2、SATA Expressなどのストレージコネクタにも使用されています。

建築

概念的には、PCI Express バスは、従来の PCI/PCI-X バスを高速シリアルに置き換えたものである。 [ 8 ] PCI Express バスと従来の PCI の主な違いの 1 つは、バス トポロジである。PCI は、PCI ホストとすべてのデバイスがアドレス、データ、および制御ラインの共通セットを共有する共有パラレルバスアーキテクチャを使用する。これとは対照的に、PCI Express はポイントツーポイントトポロジに基づいており、すべてのデバイスがルート コンプレックス(ホスト) に個別のシリアルリンクで接続される。共有バス トポロジであるため、従来の PCI バスへのアクセスは調停され (マスターが複数ある場合)、一度に 1 つのマスターにのみ、一方向に制限される。さらに、従来の PCI クロッキング スキームでは、バス トランザクションに関係するデバイスに関係なく、バス クロックがバス上の最も低速な周辺装置に制限される。これとは対照的に、PCI Express バス リンクは、任意の 2 つのエンドポイント間で全二重通信をサポートし、複数のエンドポイント間での同時アクセスに固有の制限はない。

バスプロトコルの観点から見ると、PCI Express 通信はパケットにカプセル化されています。データおよびステータスメッセージのトラフィックのパケット化とデパケット化は、PCI Express ポートのトランザクション層(後述)によって処理されます。電気信号とバスプロトコルの根本的な違いにより、異なる機械的フォームファクタと拡張コネクタ(つまり、新しいマザーボードと新しいアダプタボード)の使用が必要になります。PCI スロットと PCI Express スロットは互換性がありません。ソフトウェアレベルでは、PCI Express はPCI との下位互換性を維持しています。従来の PCI システムソフトウェアは、PCI Express 規格を明示的にサポートしていなくても、新しい PCI Express デバイスを検出して構成できますが、新しい PCI Express 機能にはアクセスできません。

2 つのデバイス間の PCI Express リンクは、1 レーンから 16レーンまでのサイズにすることができます。マルチレーン リンクでは、パケット データがレーン全体にストライプ化され、ピーク データ スループットは全体的なリンク幅に応じて増減します。レーン数はデバイスの初期化中に自動的にネゴシエートされ、いずれかのエンドポイントで制限できます。たとえば、シングル レーンの PCI Express (×1) カードをマルチレーン スロット (×4、×8 など) に挿入すると、初期化サイクルで相互にサポートされている最大のレーン数を自動ネゴシエートします。リンクは動的にダウンコンフィグレーションして使用するレーン数を減らすことができるため、不良レーンや信頼できないレーンがある場合でも耐障害性が得られます。PCI Express 規格では、×1、×2、×4、×8、×16 のリンク幅が定義されています。PCIe 5.0 までの×12、×32 リンクも定義されていますが、事実上使用されることはありませんでした。[ 9 ]これにより、PCI Expressバスは、高スループットを必要としないコスト重視のアプリケーションと、3Dグラフィックス、ネットワーキング(10ギガビットイーサネットまたはマルチポートギガビットイーサネット)、エンタープライズストレージ(SASまたはファイバーチャネル)などのパフォーマンスが重視されるアプリケーションの両方に対応できます。スロットとコネクタはこれらの幅のサブセットに対してのみ定義されており、その間のリンク幅は、次に大きい物理スロットサイズを使用します。

参考までに、PCI-X(133 MHz 64ビット)デバイスと4レーン(×4)を使用するPCI Express 1.0デバイスのピーク単方向転送速度は、ほぼ同等の1064 MB/秒です。複数のデバイスが同時にデータを転送する場合、またはPCI Express周辺機器との通信が双方向である場合、PCI ExpressバスはPCI-Xバスよりも優れたパフォーマンスを発揮する可能性があります。

相互接続

PCI Expressデバイスは、インターコネクト[ 10 ]またはリンクと呼ばれる論理接続を介して通信します。リンクは2つのPCI Expressポート間のポイントツーポイント通信チャネルであり、両方のポートで通常のPCIリクエスト(構成、I/O、メモリの読み書き)と割り込み(INTx、MSI、またはMSI-X)を送受信できます。物理レベルでは、リンクは1つまたは複数のレーンで構成されます。[ 10 ]低速周辺機器(802.11 Wi-Fiカードなど)はシングルレーン(×1)リンクを使用し、グラフィックスアダプタは通常、はるかに幅が広く、したがって高速な16レーン(×16)リンクを使用します。

レーン

レーンは2つの差動信号ペアで構成され、1つのペアはデータ受信用、もう1つのペアは送信用です。したがって、各レーンは4本のワイヤまたは信号トレースで構成されます。概念的には、各レーンは全二重バイトストリームとして使用され、リンクのエンドポイント間で8ビットの「バイト」形式のデータパケットを同時に双方向に転送します。[ 11 ] PCI Expressの物理リンクには、1、4、8、または16レーンが含まれます。[ 12 ] [ 6 ] : 4、5 [ 10 ]レーン数は「x」の接頭辞で表されます(たとえば、「×8」は8レーンのカードまたはスロットを表します)。一般的に使用される最大サイズは×16です。[ 13 ]レーンサイズは「幅」または「バイ」という用語でも表されます。たとえば、8レーンのスロットは「バイ8」または「8レーン幅」と呼ばれることがあります。

メカニカルカードのサイズについては以下を参照してください。

シリアルバス

従来のパラレル バスでは、半二重動作、信号数過剰、タイミング スキューによる帯域幅の本質的低下など、固有の制限があるため、ボンディング シリアルバスアーキテクチャが選択されました。タイミング スキューは、パラレル インターフェース内の個別の電気信号が、異なる長さの導体、場合によっては異なるプリント基板(PCB) 層、および場合によっては異なる信号速度で伝送されることによって発生します。パラレル インターフェース上の信号は、単一ワードとして同時に送信されますが、伝送時間が異なり、宛先に届く時間も異なります。インターフェース クロック周期が信号到着間の最大時間差よりも短い場合、送信されたワードを復元することはできなくなります。パラレル バス上のタイミング スキューは数ナノ秒に達することがあるため、結果として生じる帯域幅の制限は数百メガヘルツの範囲になります。

シリアルインターフェースでは、各レーン内に各方向に差動信号が 1 つしか存在しないためタイミングスキューは発生せず、また、クロック情報がシリアル信号自体に埋め込まれているため外部クロック信号は存在しません。そのため、シリアル信号の一般的な帯域幅制限は、数ギガヘルツの範囲になります。 PCI Express は、パラレルバスをシリアル相互接続に置き換えるという一般的な傾向の一例です。その他の例としては、シリアル ATA (SATA)、USB、シリアル接続 SCSI (SAS)、FireWire (IEEE 1394)、RapidIOなどがあります。デジタルビデオでは、 DVI、HDMI、DisplayPortなどが一般的な例として挙げられますが、これらはパラレルバスではなくアナログ VGA の代替品でした。

マルチチャネル シリアル設計により、低速デバイスに少ないレーンを割り当てることができるため、柔軟性が向上します。

フォームファクター

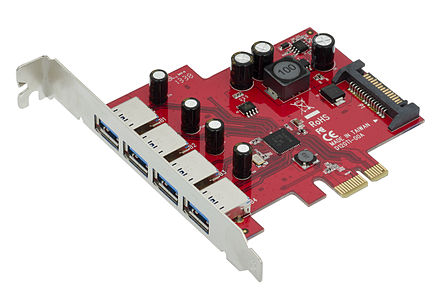

PCI Expressアドインカード

PCI Expressアドインカードは、その物理サイズ以上のスロット(最大は×16)に装着できますが、それより小さいPCI Expressスロットには装着できない場合があります。例えば、×16カードは×4または×8スロットには装着できない場合があります。一部のスロットでは、物理的に長いカードに対応し、最適な電気的および論理的接続をネゴシエートするために、オープンエンドソケットを採用しています。

スロットに実際に接続されるレーン数は、物理的なスロットサイズでサポートされるレーン数よりも少ない場合があります。例えば、×4で動作する×16スロットは、×1、×2、×4、×8、または×16のカードに対応しますが、レーン数は4つしか提供されません。仕様では「×16(×4モード)」または「×16(×4信号)」と表記される場合もありますが、「機械的 @ 電気的」表記(例:「×16 @ ×4」)も一般的です。このようなスロットの利点は、マザーボードのハードウェアでフル転送速度をサポートする必要なく、より幅広いPCI Expressカードに対応できることです。標準的な機械的サイズは×1、×4、×8、×16です。標準的な機械的サイズ以外のレーン数を使用するカードは、物理的に次に大きい機械的サイズに適合する必要があります(例:×2カードは×4サイズ、×12カードは×16サイズを使用します)。

カード自体は様々なサイズで設計・製造されています。例えば、PCI Expressカードとして提供されるソリッドステートドライブ(SSD)では、カードの物理的な寸法を表すために、 HHHL(ハーフハイト、ハーフレングス)やFHHL(フルハイト、ハーフレングス)がよく使用されます。「フル」と「ハーフ」の高さと長さの概念は、従来のPCIから継承されています。[ 15 ] [ 16 ]

| PCIカードタイプ | 寸法 | 注記 | ||

|---|---|---|---|---|

| (ミリメートル) | (で) | |||

| 身長 | 標準(フル) | 111.15 | 4.376 | 3U シャーシに適合します。 |

| ロープロファイル(ハーフ) | 68.90 | 2.731 | 2U シャーシに適合します。 | |

| 長さ | 満杯 | 312.00 | 4.376 × 12.283 | ×16に十分なスペース。 |

| 4分の3 | 254.00 | 4.376 × 10.00 | ×16に十分なスペース。 | |

| 半分 | 167.65 | 4.376 × 6.60 | ×16に十分なスペース。 | |

| 幅 | シングルスロット | 18.71 | 0.737 | 回転すると 1U シャーシに適合します。 |

| デュアルスロット | 39.04 | 1.537 | 回転すると 1U シャーシに適合します。 | |

| トリプルスロット | 59.36 | 2.337 | 回転すると 2U シャーシに適合します。 | |

フルサイズ以外の長さレベルはPCIe規格ではなく、メーカー間の合意事項です。ハーフサイズは×16コネクタを装着するのに十分なスペースを提供します。それ以下の場合は、より狭いデータコネクタを使用する必要があります。

これらのディメンションは自由に組み合わせることができますが、より大きなディメンションが共存する傾向があります。

コネクタのキーノッチ(データと電源を繋ぐ中央の突起)とカード端の間の距離は57.15ミリメートル(2.250インチ)固定です。この距離は、コンピュータケースへの取り付け用ネジ穴を備えたエンドプレートで覆われている場合があります。この固定距離により、カードがシャーシから突出することはありません。

ATXマザーボードのスロット間隔はちょうど 0.8 インチ (20 mm) です。

スロットの詳細な仕様については、以下の「#物理層」を参照してください。

非標準ビデオカードフォームファクター

最近の( 2012年頃以降[ 18 ])ゲーミングビデオカードは、数百ワットの熱を発することが多く、より高性能で静かな冷却ファンが必要となるため、PCI Express規格で規定された高さと厚さを超えているのが一般的です。 [ 19 ]最近のコンピュータケースは、これらの背の高いカードに対応するために幅が広くなっていることがよくありますが、常にそうだとは限りません。フルレングスのカード(312 mm)は珍しいため、最近のケースでは収容できない場合があります。これらのカードの厚さは、通常2~5 [ 20 ] PCIeスロット分のスペースも占めます。実際、カードの測定方法さえもベンダーによって異なり、金属ブラケットのサイズを寸法に含めるものもあれば、含めないものもあります。

例えば、2020年に発売された3つのハイエンドビデオカードを比較すると、Sapphire Radeon RX 5700 XTカードの高さは135 mm(金属ブラケットを除く)で、PCIe標準の高さを28 mm超えています。[ 21 ] XFXの別のRadeon RX 5700 XTカードは厚さ55 mm(つまり、20.32 mmでPCIスロット2.7個分)で、PCIeスロットを3つ占有しています。[ 22 ] Asus GeForce RTX 3080ビデオカードは2スロットを占有し、サイズは140.1 mm × 318.5 mm × 57.8 mmで、それぞれPCI Expressの最大高さ、長さ、厚さを超えています。[ 23 ]

ピン配置

以下の表は、PCI Expressカードのエッジコネクタの各面にある導体を示しています。プリント基板(PCB)のはんだ付け面がA面、部品面がB面です。[ 24 ] PRSNT1#ピンとPRSNT2#ピンは、ホットプラグされたカードが完全に挿入されていることを確認するために、他のピンよりもわずかに短くする必要があります。WAKE#ピンはコンピュータを起動するために最大電圧を使用しますが、カードがウェイク対応であることを示すために、スタンバイ電源からハイにプルアップする必要があります。[ 25 ]

| ピン | サイドB | A面 | 説明 | ピン | サイドB | A面 | 説明 | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12V | PRSNT1# | 最も遠いPRSNT2#ピンに接続する必要があります | 50 | HSOp(8) | 予約済み | レーン8はデータを送信します、+と- | |

| 2 | +12V | +12V | 主電源ピン | 51 | HSOn(8) | 地面 | ||

| 3 | +12V | +12V | 52 | 地面 | HSIp(8) | レーン8受信データ、+と- | ||

| 4 | 地面 | 地面 | 53 | 地面 | HSIn(8) | |||

| 5 | SMCLK | TCK | SMBusおよびJTAGポートピン | 54 | HSOp(9) | 地面 | レーン9はデータを送信します、+と- | |

| 6 | SMDAT | TDI | 55 | HSOn(9) | 地面 | |||

| 7 | 地面 | TDO | 56 | 地面 | HSIp(9) | レーン9受信データ、+と- | ||

| 8 | +3.3V | TMS | 57 | 地面 | HSIn(9) | |||

| 9 | TRST# | +3.3V | 58 | HSOp(10) | 地面 | レーン10はデータを送信します、+と- | ||

| 10 | +3.3 V補助電源 | +3.3V | 補助電源とスタンバイ電源 | 59 | HSOn(10) | 地面 | ||

| 11 | ウェイク# | パースト# | リンクの再活性化; 根本的なリセット[ 26 ] | 60 | 地面 | HSIp(10) | レーン10受信データ、+と- | |

| キーノッチ | 61 | 地面 | HSIn(10) | |||||

| 12 | CLKREQ# | 地面 | クロック要求信号[ 27 ] | 62 | HSOp(11) | 地面 | レーン11はデータを送信します、+と- | |

| 13 | 地面 | REFCLK+ | 基準クロック差動ペア | 63 | HSOn(11) | 地面 | ||

| 14 | HSOp(0) | REFCLK− | レーン0送信データ、+と- | 64 | 地面 | HSIp(11) | レーン11はデータ受信、+と- | |

| 15 | HSOn(0) | 地面 | 65 | 地面 | HSIn(11) | |||

| 16 | 地面 | HSIp(0) | レーン0受信データ、+および- | 66 | HSOp(12) | 地面 | レーン12はデータを送信します、+と- | |

| 17 | PRSNT2# | HSIn(0) | 67 | HSOn(12) | 地面 | |||

| 18 | 地面 | 地面 | 68 | 地面 | HSIp(12) | レーン12はデータ受信、+と- | ||

| PCI Express ×1 カードはピン 18 で終了します | 69 | 地面 | HSIn(12) | |||||

| 19 | HSOp(1) | 予約済み | レーン1はデータを送信します、+と- | 70 | HSOp(13) | 地面 | レーン13はデータを送信します、+と- | |

| 20 | HSOn(1) | 地面 | 71 | HSOn(13) | 地面 | |||

| 21 | 地面 | HSIp(1) | レーン1受信データ、+と- | 72 | 地面 | HSIp(13) | レーン13はデータ受信、+と- | |

| 22 | 地面 | HSIn(1) | 73 | 地面 | HSIn(13) | |||

| 23 | HSOp(2) | 地面 | レーン2はデータを送信します、+と- | 74 | HSOp(14) | 地面 | レーン14はデータを送信します、+と- | |

| 24 | HSOn(2) | 地面 | 75 | HSOn(14) | 地面 | |||

| 25 | 地面 | HSIp(2) | レーン2受信データ、+と- | 76 | 地面 | HSIp(14) | レーン14はデータ受信、+と- | |

| 26 | 地面 | HSIn(2) | 77 | 地面 | HSIn(14) | |||

| 27 | HSOp(3) | 地面 | レーン3はデータを送信します、+と- | 78 | HSOp(15) | 地面 | レーン15はデータを送信します、+と- | |

| 28 | HSOn(3) | 地面 | 79 | HSOn(15) | 地面 | |||

| 29 | 地面 | HSIp(3) | レーン3はデータ受信、+と-「パワーブレーキ」、デバイスの電力を削減するためのアクティブロー | 80 | 地面 | HSIp(15) | レーン15はデータ受信、+と- | |

| 30 | パワーブレーキ# | HSIn(3) | 81 | PRSNT2# | HSIn(15) | |||

| 31 | PRSNT2# | 地面 | 82 | 予約済み | 地面 | |||

| 32 | 地面 | 予約済み | ||||||

| PCI Express ×4 カードはピン 32 で終了します。 | ||||||||

| 33 | HSOp(4) | 予約済み | レーン4はデータを送信します、+と- | |||||

| 34 | HSOn(4) | 地面 | ||||||

| 35 | 地面 | HSIp(4) | レーン4はデータ受信、+と- | |||||

| 36 | 地面 | HSIn(4) | ||||||

| 37 | HSOp(5) | 地面 | レーン5はデータを送信します、+と- | |||||

| 38 | HSOn(5) | 地面 | ||||||

| 39 | 地面 | HSIp(5) | レーン5はデータ受信、+と- | |||||

| 40 | 地面 | HSIn(5) | ||||||

| 41 | HSOp(6) | 地面 | レーン6はデータを送信します、+と- | |||||

| 42 | HSOn(6) | 地面 | ||||||

| 43 | 地面 | HSIp(6) | レーン6受信データ、+と- | 伝説 | ||||

| 44 | 地面 | HSIn(6) | 力 | カードに電力を供給する | ||||

| 45 | HSOp(7) | 地面 | レーン7はデータを送信します、+と- | センス | カードにまとめる | |||

| 46 | HSOn(7) | 地面 | 地面 | ゼロボルト基準 | ||||

| 47 | 地面 | HSIp(7) | レーン7受信データ、+と- | 開いた排水口 | 低く引かれたり、複数のカードによって感知される可能性がある[ 28 ] | |||

| 48 | PRSNT2# | HSIn(7) | ホストからカードへ | マザーボードからカードへの信号 | ||||

| 49 | 地面 | 地面 | カードからホストへ | カードからマザーボードへの信号 | ||||

| PCI Express ×8カードはピン49で終了します | 予約済み | 現在使用されていない | ||||||

力

スロットパワー

すべてのPCI Expressカードは最大3A で+3.3 V (9.9 W)。+12 Vの消費量と総電力は、カードのフォームファクタと役割によって異なります。[ 30 ] : 35–36 [ 31 ] [ 32 ]

- ×1 カードは、+12 V (6 W)で 0.5 A、合計で 10 W に制限されます。

- ×4 以上のカードは、+12 V (25 W) で 2.1 A、合計で 25 W に制限されます。

- フルサイズの ×1 カードは、初期化および高電力デバイスとしてのソフトウェア構成後に、最大 25 W の制限まで消費する場合があります。

- フルサイズの×16グラフィックカードは、 初期化と高電力デバイスとしてのソフトウェア設定後、+12Vで最大5.5A(66W)、合計で75Wを消費することがあります。[ 25 ]:38–39

6ピンおよび8ピン電源コネクタ

オプションのコネクタを追加75 W (6ピン) または150 W(8ピン)+12 V電源、最大合計300W (75W×2 + 150W×1)。

- Sense0 ピンはケーブルまたは電源によってグランドに接続されるか、ケーブルが接続されていない場合はボード上で浮いた状態になります。

- Sense1 ピンはケーブルまたは電源によってグランドに接続されるか、ケーブルが接続されていない場合はボード上で浮いた状態になります。

一部のカードでは8ピンコネクタを2つ使用し、合計375W(75W×1 + 150W×2)の電力供給が可能です。これは2018年のPCI Express 4.0 CEMで新たに標準化されましたが、それ以前から既に使用されていました。[ 17 ] 8ピンPCI Expressコネクタは、主にSMPおよびマルチコアシステムの電源供給に使用されるEPS12Vコネクタと混同しないでください。これらの電源コネクタは、Molex Mini-Fit Jr.シリーズコネクタの派生型です。[ 33 ]

| ピン | PSケーブルの メス/レセプタクル | PCB上のオス/直角ヘッダー |

|---|---|---|

| 6ピン | 45559-0002 | 45558-0003 |

| 8ピン | 45587-0004 | 45586-0005, 45586-0006 |

| 6ピン電源コネクタ(75 W)[ 34 ] | 8ピン電源コネクタ(150W)[ 35 ] [ 36 ] [ 37 ] |   | |||

|---|---|---|---|---|---|

| ピン | 説明 | ピン | 説明 | ||

| 1 | +12V | 1 | +12V | ||

| 2 | 接続されていません(通常は+12 Vも同様) | 2 | +12V | ||

| 3 | +12V | 3 | +12V | ||

| 4 | センス1(8ピン接続[ A ]) | ||||

| 4 | 地面 | 5 | 地面 | ||

| 5 | センス | 6 | センス0(6ピンまたは8ピン接続) | ||

| 6 | 地面 | 7 | 地面 | ||

| 8 | 地面 | ||||

- ^ 6 ピン コネクタを 8 ピン レセプタクルに接続すると、 Sense1がないため、カードには最大 75 W までしか使用できないことが

12VHPWRコネクタ

.jpg/440px-2023_Adapter_NVIDIA_12VHPWR_(2).jpg)

16ピン12VHPWRコネクタは、グラフィックス・プロセッシング・ユニット(GPU)をコンピュータ電源に接続し、最大600Wの電力を供給するための規格です。NVIDIAは2022年に、従来のGPU用6ピンおよび8ピン電源コネクタに代わるコネクタとして導入しました。その目的は、NVIDIA GPUの増大する電力要件に対応することでした。このコネクタは、PCI Express 5の一部として正式に採用されました。[ 38 ]

このコネクタは、2023年にPCIe CEM 5.1およびPCIe ECN 6.0で導入された12V-2x6と呼ばれるマイナーリビジョンに置き換えられました。 [ 39 ] [ 40 ]このリビジョンでは、GPU側とPSU側のソケットが変更され、センスピンが電源ピンが正しく接続された場合にのみ接触するようになりました。ケーブルとプラグは変更されていません。[ 41 ]この変更は部分的な接触による溶融を防ぐことを目的としていますが、この新しいソケットを搭載したGPUでは溶融が引き続き報告されています。[ 42 ]新しいセンスピンが追加されたことで、電源ネゴシエーションに大きな変更が加えられました。[ 43 ]

12VHPWRコネクタには「H+」記号が付いていますが、12V-2x6コネクタには「H++」記号が付いています。[ 44 ]

48VHPWRコネクタ

2021年、PCIeカード電気機械(CEM、「ケミストリー」の「ケム」のように発音)仕様において、2つの通電接点と4つのセンスピンを備えた48V用コネクタが導入されました。これは2023年のPCIe-CEM 5.1にも引き継がれました。[ 45 ]接点の定格電流は15Aです。48VHPWRコネクタは720ワットを流すことができます。

| P1 | P2 | ||

|---|---|---|---|

| +48V(15A) | アース(15A) | ||

| S1 | シーズン2 | S3 | S4 |

| カード電源安定 | カード_CBL_PRES# | センス0 | センス1 |

その後、これは削除され、Sense0 と Sense1 が互いに最も離れた位置に配置される互換性のない 48V 1×2 コネクタが導入されました。

パワーエクスカーション

電力エクスカーションとは、定格最大(持続)電力レベルを超える短時間の電力消費ピークを指します。PCIe-CEM 5.0への追加エンジニアリング変更通知(ECN)以降、追加の電源コネクタは、最大持続電力の3倍で100マイクロ秒の電力消費を処理でき、対数直線に従って1秒のウィンドウレベルで1倍に減少する必要があります。PCIe-ECM 5.1以降、スロット電源も同様にエクスカーション拡張され、100マイクロ秒で2.5倍になります。CEM 5.1では、追加されたエクスカーション制限はソフトウェア設定、具体的にはSet_Slot_Power_Limitメッセージ後にのみ提供されます。ECNはATX 3.0の一部であり、PCIe CEM 5.1はATX 3.1の一部です。[ 46 ]

PCI Express ミニカード

PCI Expressミニカード( Mini PCI Express、Mini PCIe、Mini PCI-E、mPCIe、PEMとも呼ばれる)は、PCI ExpressをベースにしたMini PCIフォームファクタの代替品です。PCI -SIGによって開発されました。ホストデバイスはPCI ExpressとUSB 2.0の両方の接続をサポートしており、各カードはどちらの規格も使用できます。2005年以降に製造されたほとんどのノートパソコンは、拡張カードにPCI Expressを使用していますが、2015年現在、多くのベンダーがこの用途に新しいM.2フォームファクタを採用する方向に移行しています。[ 47 ]

PCI Expressミニカードは寸法が異なるため、標準のフルサイズPCI Expressスロットと物理的に互換性がありません。ただし、フルサイズスロットで使用できるようにするパッシブアダプターが存在します。[ 48 ]

物理的な寸法

PCI Expressミニカードの寸法は、フルミニカードで30 mm × 50.95 mm(幅 × 長さ)です。52ピンのエッジコネクタは、0.8 mmピッチで2列に交互に配置されています。各列には8つのコンタクトがあり、4つのコンタクトに相当するギャップがあり、さらに18のコンタクトがあります。ボードの厚さは、部品を除いて1.0 mmです。「ハーフミニカード」(HMCと略されることもあります)も規定されており、これは物理的な長さの約半分、26.8 mmです。また、フルサイズのミニPCIeカードの約半分の長さである30 × 31.90 mmのハーフサイズのミニPCIeカードもあります。[ 49 ] [ 50 ]

電気インターフェース

PCI Express ミニ カード エッジ コネクタは、複数の接続とバスを提供します。

- PCI Express ×1(SMBus付き)

- USB 2.0

- コンピュータのシャーシ上のワイヤレスネットワーク(Wi-Fiなど)ステータスの診断LEDへの配線

- GSMおよびWCDMAアプリケーション用のSIMカード(UIM 信号は仕様どおり)

- 将来的に別の PCIe レーンを拡張可能

- 1.5 Vおよび3.3 V電源

Mini-SATA (mSATA) バリアント

Mini PCI Expressフォームファクタを共有しているにもかかわらず、mSATAスロットは必ずしもMini PCI Expressと電気的に互換性があるわけではない。このため、mSATAドライブと互換性があるのは特定のノートパソコンだけである。互換性のあるシステムのほとんどは、Huron Riverプラットフォームを使用したIntelのSandy Bridgeプロセッサアーキテクチャに基づいている。2011年3月から4月にリリースされたLenovoのThinkPad T、W、Xシリーズなどのノートパソコンは、WWANカードスロットでmSATA SSDカードをサポートしています。ThinkPad Edge E220s/E420s、Lenovo IdeaPad Y460/Y560/Y570/Y580もmSATAをサポートしています。[ 51 ]逆に、LシリーズなどはWWANスロットでPCIe規格を使用するM.2カードのみをサポートします。

一部のノートパソコン(特にAsus Eee PC、Apple MacBook Air、Dell mini9およびmini10)は、PCI Express Mini Cardの派生版をSSDとして採用しています。この派生版は、予約済みピンといくつかの非予約ピンを使用してSATAおよびIDEインターフェースのパススルーを実装し、USB、グランドライン、そして場合によってはコアとなるPCIe ×1バスのみをそのまま使用します。[ 52 ]このため、ネットブック向けに販売されている「miniPCIe」フラッシュドライブやソリッドステートドライブは、真のPCI Express Mini実装とはほとんど互換性がありません。

また、Asusの一般的なminiPCIe SSDは71mmの長さであるため、Dellの51mmモデルはしばしば(誤って)ハーフサイズと称されます。真の51mm Mini PCIe SSDは2009年に発表され、2層構造のPCBを搭載することで大容量ストレージを実現しました。発表された設計ではPCIeインターフェースが維持されているため、標準的なmini PCIeスロットと互換性があります。しかし、実際に動作する製品は未だ開発されていません。

インテルは、PCIe ×1 ミニカードスロットを備えたデスクトップボードを多数提供していますが、通常、mSATA SSD をサポートしていません。PCIe ×1 ミニカードスロット(通常はSATAポートと多重化)でmSATAをネイティブサポートするデスクトップボードのリストは、インテルサポートサイトに掲載されています。[ 53 ]

PCI エクスプレス M.2

M.2はmSATA規格とMini PCIeに代わる規格です。[ 54 ] M.2コネクタで提供されるコンピュータバスインターフェースは、PCI Express 3.0以上(最大4レーン)、Serial ATA 3.0、USB 3.0(後者2つはそれぞれ1つの論理ポート)です。M.2ホストまたはデバイスのメーカーは、必要なホストサポートレベルとデバイスの種類に応じて、どのインターフェースをサポートするかを選択します。

PCI Express 外部ケーブル

PCI Express外部ケーブル(外部PCI Express、ケーブル付きPCI Express、ePCIeとも呼ばれる)仕様は、2007年2月にPCI-SIGによってリリースされました。 [ 55 ] [ 56 ]

標準ケーブルとコネクタは、×1、×4、×8、×16のリンク幅で定義されており、転送速度はレーンあたり250MB/秒です。PCI-SIGは、PCI Express 2.0と同様に、この規格が500MB/秒に達すると予測しています。ケーブル接続されたPCI Expressの用途例としては、複数のPCIeスロットとPCIe-ePCIeアダプタ回路を内蔵した金属製の筐体が挙げられます。このデバイスは、ePCIe仕様がなければ実現不可能でした。

PCI エクスプレス OCuLink

OCuLink(「optical-copper link」の略で、Cuは銅の化学記号です)は、「PCI Expressのケーブル版」の拡張機能です。2015年10月にリリースされたOCuLinkバージョン1.0は、銅線ケーブルで最大4レーン(3.9 GB/秒)のPCIe 3.0をサポートします。将来的には 光ファイバー版も登場する可能性があります。

OCuLinkの最新バージョンであるOCuLink-2は、8GB/秒または16GB/秒(PCIe 4.0×4または×8)[ 57 ]をサポートしていますが、 USB4 v2.0またはThunderbolt 5接続の最大帯域幅は10GB/秒です。

OCulinkは主にサーバー内のPCIe(またはSATAブレイクアウト)相互接続を目的としていますが、ラップトップの外付けGPUボックスの接続にも限定的に採用されています。[ 58 ]

派生形

PCIe を使用する、または使用できるフォームファクタは他にも多数あります。具体的には、以下のフォームファクタが挙げられます。

- 低背カード

- ExpressCard : PC カードフォーム ファクタの後継(×1 PCIe および USB 2.0 搭載、ホットプラグ可能)

- PCI Express ExpressModule: サーバーおよびワークステーション向けに定義されたホットプラグ可能なモジュラーフォームファクター

- XQDカード: CompactFlash AssociationによるPCI Expressベースのフラッシュカード規格で、×2 PCIeを搭載

- CFexpressカード: CompactFlash Association による PCI Express ベースのフラッシュ カード。1 ~ 4 の PCIe レーンをサポートする 3 つのフォーム ファクタがあります。

- SDカード: SD仕様のバージョン7.0で導入されたSD Expressバスは、×1 PCIeリンクを使用します。

- XMC : CMC / PMCフォームファクタに類似(VITA 42.3)

- AdvancedTCA :大規模アプリケーション向けのCompactPCIを補完するものであり、シリアルベースのバックプレーン トポロジをサポートします。

- AMC : AdvancedTCA仕様を補完し、ATCA ボード (×1、×2、×4、または ×8 PCIe) 上のプロセッサおよび I/O モジュールをサポートします。

- FeaturePak : 組み込みおよび小型フォームファクタアプリケーション向けの小型拡張カードフォーマット(43 mm × 65 mm)で、高密度コネクタに 2 つの ×1 PCIe リンク、USB、I2C、および最大 100 ポイントの I/O を実装します。

- ユニバーサルIO :スーパーマイクロコンピュータ社の薄型ラックマウントシャーシ用に設計された派生型。 [ 59 ]コネクタブラケットが逆さまになっているため、通常のPCI Expressソケットには適合しませんが、ピン互換性があり、ブラケットを取り外せば挿入できます。

- M.2(旧称NGFF)

- M-PCIeは、 M-PHY物理層を介してPCIe 3.0をモバイルデバイス(タブレットやスマートフォンなど)に提供します。 [ 60 ] [ 61 ]

- シリアル接続SCSI関連ポート:

- SATA Express、U.2(旧称SFF-8639)、U.3は同じポートを使用します

- スリムSAS(SFF-8654)

- SFF-TA-1016(M-XIOコネクタ)

- SFF-TA-1026、SFF-TA-1033

PCIeスロットコネクタは、PCIe以外のプロトコルも伝送できます。一部の9xxシリーズIntelチップセットは、シリアルデジタルビデオ出力をサポートしています。これは、PCIeではなく、ホストCPUの統合グラフィックスからビデオ信号をスロットを介して送信する独自の技術で、対応するアドインを使用しています。

PCIe トランザクション層プロトコルは、電気的には PCIe ではない他の相互接続でも使用できます。

- Thunderbolt : Intelによるロイヤリティフリー(Thunderbolt 3以降)の相互接続規格で、Mini DisplayPortと互換性のあるフォームファクターでDisplayPortとPCIeプロトコルを統合しています。Thunderbolt 3.0はUSB 3.1も統合し、 Mini DisplayPortではなく USB-Cフォームファクターを採用しています。

歴史と改訂

PCIeは開発初期段階ではHSI(High Speed Interconnect )と呼ばれていましたが、その後3GIO(第3世代I/O )へと名称が変更され、最終的にPCI-SIGの名称であるPCI Expressに落ち着きました。Arapaho Work Group (AWG)と呼ばれる技術ワーキンググループが規格を策定しました。当初の草案では、AWGはIntelのエンジニアのみで構成されていましたが、その後、業界パートナーも加わり拡大しました。

それ以来、PCIe は大規模な改訂や小規模な改訂を何度か実施し、パフォーマンスやその他の機能が向上しました。

比較表

| バージョン | 年 | ラインコード | 転送速度(レーンあたり)[ i ] [ ii ] | スループット(GB/秒)[ i ] [ iii ] | |||||

|---|---|---|---|---|---|---|---|---|---|

| ×1 | ×2 | ×4 | ×8 | ×16 | |||||

| 1.0 | 2003 | NRZ | 8b/10b | 2.5 GT/秒 | 0.25 | 0.5 | 1 | 2 | 4 |

| 2.0 | 2007 | 5.0 GT/秒 | 0.5 | 1 | 2 | 4 | 8 | ||

| 3.0 | 2010 | 128b/130b | 8.0 GT/秒 | 0.985 | 1.969 | 3.938 | 7.877 | 15.754 | |

| 4.0 | 2017 | 16.0 GT/秒 | 1.969 | 3.938 | 7.877 | 15.754 | 31.508 | ||

| 5.0 | 2019 | 32.0 GT/秒 | 3.938 | 7.877 | 15.754 | 31.508 | 63.015 | ||

| 6.0 | 2022年(初回実施は2025年) | PAM-4 FEC | 1b/1b 242B/256Bフリット | 64.0 GT/秒 | 7.563 | 15.125 | 30.25 | 60.5 | 121 |

| 7.0 | 2025年(仕様公開) | 128.0 GT/秒 | 15.125 | 30.25 | 60.5 | 121 | 242 | ||

| 8.0 | 2028年(予定) | 256.0 GT/秒 | 30.25 | 60.5 | 121 | 242 | 484 | ||

- 注記

- ^ a b各方向(各レーンはデュアル シンプレックス チャネルです)。

- ^転送速度はエンコードされたシリアル ビット レートを指します。2.5 GT/s は 2.5 Gbit/s のシリアル データ レートを意味します。

- ^スループットは使用可能な帯域幅を示します(つまり、ペイロードのみを含み、8b/10b、128b/130b、または242B/256Bエンコーディングのオーバーヘッドは含みません)。PCIe 1.0のレーンあたり2.5 GT/sの転送速度は、2.5 Gbit/sのシリアルビットレートを意味します。8b/10bエンコーディングを適用すると、2.0 Gbit/s = 250 MB/sの実効スループットに相当します。

PCI エクスプレス 1.0a

2003 年に、PCI-SIG は、レーンあたりのデータ レートが 0.25ギガバイト/秒(GB/秒)、転送レートが 2.5ギガトランスファー/秒(GT/秒) の PCIe 1.0a を導入しました。

転送速度は、ビット/秒ではなく転送回数/秒で表されます。これは、転送回数には追加のスループットを提供しないオーバーヘッドビットが含まれるためです。[ 65 ] PCIe 1.xは8b/10bエンコード方式を採用しており、その結果、生のチャネル帯域幅に20%(= 2/10)のオーバーヘッドが生じます。[ 66 ]そのため、PCIeの用語では、転送速度はエンコードされたビットレートを指します。2.5GT/sは、エンコードされたシリアルリンクでは2.5Gbit/sです。これは、プリコードされたデータでは2.0Gbit/s、PCIeではスループットと呼ばれる0.25GB/sに相当します。

PCIエクスプレス1.1

2005年、PCI-SIG [ 67 ]はPCIe 1.1を発表しました。この更新された仕様には、明確化といくつかの改良が含まれていますが、PCI Express 1.0aと完全に互換性があります。データレートには変更はありません。

PCIエクスプレス2.0

PCI-SIGは2007年1月15日にPCI Express Base 2.0仕様の公開を発表しました。[ 68 ] PCIe 2.0規格では、PCIe 1.0と比較して転送速度が2倍の 5GT/sとなり、レーンあたりのスループットは250MB/sから500MB/sに向上します。その結果、16レーンのPCIeコネクタ(×16)は、最大8GB/sのスループットをサポートできます。

PCIe 2.0マザーボードスロットは、PCIe v1.xカードと完全な下位互換性があります。PCIe 2.0カードは、PCI Express 1.1の利用可能な帯域幅を使用するため、PCIe 1.xマザーボードとも基本的に下位互換性があります。概して、v2.0用に設計されたグラフィックカードまたはマザーボードは、v1.1またはv1.0aでも動作します。

PCI-SIGはまた、PCIe 2.0ではポイントツーポイントデータ転送プロトコルとそのソフトウェアアーキテクチャが改善されていると述べた。[ 69 ]

インテル初のPCIe 2.0対応チップセットはX38で、 2007年10月21日より様々なベンダー( Abit、Asus、Gigabyte )からボードの出荷が開始されました。[ 70 ] AMDはAMD 700チップセットシリーズでPCIe 2.0のサポートを開始し、nVidiaはMCP72でサポートを開始しました。[ 71 ]インテルP35チップセットを含むインテルの以前のチップセットはすべてPCIe 1.1または1.0aをサポートしていました。[ 72 ]

1.x と同様に、PCIe 2.0 は8b/10b エンコーディングスキームを使用するため、レーンごとに 5 GT/s の生データ レートから最大 4 Gbit/s の有効な転送レートを実現します。

PCIエクスプレス2.1

PCI Express 2.1(2009年3月4日に仕様が公表)は、PCI Express 3.0で完全実装が予定されている管理、サポート、トラブルシューティングシステムの大部分をサポートしています。ただし、速度はPCI Express 2.0と同じです。スロットからの電力増加により、PCI Express 2.1カードと一部の旧型マザーボード(1.0/1.0a)との下位互換性は失われますが、PCI Express 1.1コネクタ搭載のマザーボードのほとんどには、メーカーからユーティリティを通じてBIOSアップデートが提供されており、PCIe 2.1カードとの下位互換性が確保されています。

PCIエクスプレス3.0

PCI Express 3.0 ベース仕様リビジョン 3.0 は、幾度かの延期を経て、2010 年 11 月に公開されました。2007 年 8 月、PCI-SIG は PCI Express 3.0 が 8ギガ転送/秒 (GT/s) のビットレートを実現し、既存の PCI Express 実装との下位互換性を維持することを発表しました。同時に、PCI Express 3.0 の最終仕様は 2010 年第 2 四半期まで延期されることも発表されました。[ 73 ] PCI Express 3.0 仕様の新機能には、送信機と受信機のイコライゼーション、 PLL の改良、クロックデータリカバリ、現在サポートされているトポロジのチャネル拡張など、信号伝達とデータ整合性を向上させるための数々の最適化が含まれていました。[ 74 ]

PCI Express 相互接続帯域幅の拡張の実現可能性に関する 6 か月間の技術分析の結果、PCI-SIG の分析では、PCI Express プロトコル スタックとの完全な互換性 (影響はごくわずか) を維持しながら、主流のシリコン プロセス テクノロジで 1 秒あたり 8 ギガ転送を実現し、既存の低コストの材料とインフラストラクチャで展開できることが判明しました。

PCI Express 3.0では、従来の8b/10bエンコード方式から128b/130bエンコード方式にアップグレードされ、帯域幅のオーバーヘッドがPCI Express 2.0の20%から約1.54%(= 2/130)に削減されました。PCI Express 3.0の8GT/sビットレートは、レーンあたり985MB/sの実効速度を実現し、PCI Express 2.0と比較してレーン帯域幅がほぼ2倍になります。[ 63 ]

2010年11月18日、PCI-SIGは、この新しいバージョンのPCI Expressをベースにしたデバイスを構築するために、最終的なPCI Express 3.0仕様を会員に正式に公開しました。[ 75 ]

PCIエクスプレス3.1

2013年9月、PCI Express 3.1仕様が2013年後半または2014年初頭にリリースされることが発表され、公開されたPCI Express 3.0仕様に電力管理、パフォーマンス、機能性の3つの分野で様々な改良が統合されました。[ 61 ] [ 76 ] 2014年11月にリリースされました。[ 77 ]

PCIエクスプレス4.0

2011年11月29日、PCI-SIGはPCI Express 4.0を暫定的に発表し、[ 78 ] 16レーン構成でPCI Express 3.0の2倍の帯域幅である各方向31.5 GB/sの16GT/sビットレートを提供しながら、ソフトウェアサポートと使用される機械インターフェースの両方で後方互換性と前方互換性を維持しました。 [ 79 ] PCI Express 4.0仕様では、 Thunderboltの代替としてOCuLink-2も導入されています。OCuLinkバージョン2は最大16GT/s( ×8レーンで合計16GB/s)ですが、[ 57 ] Thunderbolt 3リンクの最大帯域幅は5GB /sです。

2016年のPCI-SIG開発者会議では、Cadence、PLDA、SynopsysがPCIe 4.0の物理層、コントローラ、スイッチ、その他のIPブロックの開発を披露しました。[ 80 ]

メラノックステクノロジーズは 、2016年6月15日にPCIe 4.0対応の最初の100Gbit/sネットワークアダプタを発表しました。[ 81 ]また、2016年11月10日にはPCIe 4.0対応の最初の200Gbit /sネットワークアダプタを発表しました。[ 82 ]

2016年8月、シノプシスはインテル デベロッパー フォーラムにおいて、FPGA クロックでレーンを PCIe 4.0 速度で動作させるテスト セットアップを発表しました。同社の IP は、2016 年末にチップと製品を発表する予定の複数の企業にライセンス供与されています。[ 83 ]

2016年8月のIEEE Hot Chips Symposiumで、IBMはPCIe 4.0をサポートする最初のCPUであるPOWER9を発表しました。[ 84 ] [ 85 ]

PCI-SIGは2017年6月8日にPCI Express 4.0の最終仕様のリリースを正式に発表しました。[ 86 ]この仕様には柔軟性、拡張性、低消費電力の改善が含まれています。

2017年12月5日、IBMはPCIe 4.0スロットを搭載した最初のシステムであるPower AC922を発表しました。[ 87 ] [ 88 ]

NETINT Technologiesは、2018年7月17日にフラッシュメモリサミット2018に先立ち、PCIe 4.0ベースの最初のNVMe SSDを発表しました[ 89 ]

AMDは2019年1月9日、次期Zen 2ベースのプロセッサとX570チップセットがPCIe 4.0をサポートすると発表した。[ 90 ] AMDは古いチップセットの部分的なサポートを可能にすることを望んでいたが、マザーボードのトレースがPCIe 4.0仕様に準拠していないために不安定になり、それが不可能になった。[ 91 ] [ 92 ]

インテルは2020年半ばに、 Tiger Lakeマイクロアーキテクチャの一部として、PCI Express 4.0をサポートする最初のモバイルCPUをリリースしました。[ 93 ]

PCIエクスプレス5.0

2017年6月、PCI-SIGはPCI Express 5.0の暫定仕様を発表しました。[ 86 ] 帯域幅は32GT /sに増加し、 16レーン構成で各方向63GB/sを実現することが期待されていました。このドラフト仕様は2019年に標準化される予定でした。当初は技術的な実現可能性の観点から25.0GT/sも検討されていました。

2017年6月7日、PCI-SIG DevConで、シノプシスは32GT/sのPCI Express 5.0の初デモを記録しました。[ 94 ]

2018年5月31日、PLDAは同日、PCIe 5.0仕様のドラフト0.7に基づいたXpressRICH5 PCIe 5.0コントローラIPの提供開始を発表しました。[ 95 ] [ 96 ]

2018年12月10日、PCI SIGはPCIe 5.0仕様のバージョン0.9を会員にリリースしました。[ 97 ] そして2019年1月17日、PCI SIGはバージョン0.9が承認され、バージョン1.0は2019年第1四半期にリリースされる予定であると発表しました。[ 98 ]

2019年5月29日、PCI-SIGは最終的なPCI Express 5.0仕様のリリースを正式に発表しました。[ 99 ] PCI Express 5.0は、以前のバージョンのPCI Express仕様との下位互換性を維持しています。

2019年11月20日、江蘇省華村は12nm製造プロセスで最初のPCIe 5.0コントローラーHC9001を発表し[ 100 ]、2020年に生産を開始しました。

2020年8月17日、IBMはPCIe 5.0を搭載し、シングルチップモジュール(SCM)あたり最大32レーン、ダブルチップモジュール(DCM)あたり最大64レーンを備えたPower10プロセッサーを発表しました。 [ 101 ]

2021年9月9日、IBMはPower E1080エンタープライズ・サーバーを発表し、9月17日に提供開始予定でした。[ 102 ]システムあたり最大32スロットのPower10 SCMを最大16個搭載でき、PCIe 5.0 ×8またはPCIe 4.0 ×16として動作可能です。[ 103 ]また、これらはオプションの光CXPコンバーター・アダプターを外部PCIe拡張ドロワーに接続するためのPCIe 5.0 ×16スロットとしても使用できます。

2021年10月27日、インテルはPCIe 5.0(最大16レーン)接続を備えた世界初のコンシューマー向けx86-64プロセッサーである第12世代インテル Core CPUファミリーを発表しました。[ 104 ]

2022年3月22日、Nvidiaは世界初のPCIe 5.0 GPUであるNvidia Hopper GH100 GPUを発表しました。[ 105 ]

2022年5月23日、AMDはコンシューマープラットフォームで最大24レーン、サーバープラットフォームで最大128レーンのPCIe 5.0接続をサポートするZen 4アーキテクチャを発表しました。[ 106 ] [ 107 ]

PCIエクスプレス6.0

2019年6月18日、PCI-SIGはPCI Express 6.0仕様の開発を発表しました。帯域幅は64GT /sに増加し、 16レーン構成で各方向128GB/sの転送速度を実現する見込みで、2021年のリリースを目指しています。[ 108 ]この新規格では、非ゼロ復帰(NRZ)変調の代わりに、低遅延の前方誤り訂正(FEC)を備えた4レベルパルス振幅変調(PAM-4)が採用されています。[ 109 ]従来のPCI Expressバージョンとは異なり、前方誤り訂正はデータの整合性を高めるために使用され、PAM-4はラインコードとして使用されることで、1回の転送で2ビットが転送されます。64GT/sのデータ転送速度(生のビットレート)では、 ×16構成で各方向最大121GB /sの転送速度が可能です。 [ 108 ]

2020年2月24日に、PCI Express 6.0リビジョン0.5仕様(すべてのアーキテクチャの側面と要件が定義された「最初のドラフト」)がリリースされました。[ 110 ]

2020年11月5日、PCI Express 6.0リビジョン0.7仕様(テストチップで電気仕様が検証された「完全なドラフト」)がリリースされました。[ 111 ]

2021年10月6日に、PCI Express 6.0リビジョン0.9仕様(「最終草案」)がリリースされました。[ 112 ]

2022年1月11日、PCI-SIGは最終的なPCI Express 6.0仕様のリリースを正式に発表しました。[ 113 ] PCI Express 6.0は、以前のバージョンのPCI Express仕様との下位互換性を維持しています。

PAM-4符号化ではビット誤り率(BER)が10−6 (従来は10−12 )と大幅に高くなるため、128b/130b符号化の代わりに、巡回冗長検査(CRC)に加えて3ウェイインターレースフォワードエラー訂正(FEC)が使用される。固定の256バイトのフロー制御ユニット(FLIT)ブロックは、可変サイズのトランザクションレベルパケット(TLP)とデータリンク層ペイロード(DLLP)を含む242バイトのデータを伝送し、残りの14バイトは8バイトのCRCと6バイトのFEC用に予約されている。[ 114 ] [ 115 ] PAM-4/FLITモードでは誤り率を低減するために3ウェイグレイコードが使用される。インターフェースは、より低いデータレートに再トレーニングしてもNRZおよび128/130b符号化に切り替わらない。[ 116 ] [ 117 ]

PCIe 6.0ハードウェアは、最終仕様のリリースから約3年後、PCIe 7.0仕様の公開直後の2025年8月まで発売されませんでした。[118 ]この遅延は前例のないものとされ、PCWorldは長年PCIe 6.0が「紙の上だけのもの」であったと指摘しました。[ 120 ]

PCI エクスプレス 7.0

2022年6月21日、PCI-SIGはPCI Express 7.0仕様の開発を発表しました。[ 121 ]この仕様は、バージョン6.0と同じPAM4信号方式を使用し、×16構成で128GT/sの生ビットレートと最大242GB/sの双方向データ転送を実現します。チャネルパラメータを微調整することで信号損失を低減し、電力効率を向上させることでデータレートを倍増させますが、信号整合性の確保が課題となることが予想されます。仕様は2025年に最終決定される予定です。

2024年4月3日にPCI Express 7.0リビジョン0.5仕様(「最初のドラフト」)がリリースされました。[ 122 ]

2025年1月17日、PCI-SIGはPCIe 7.0仕様バージョン0.7(「完全草案」)のリリースを発表しました。[ 123 ]

2025年3月19日、PCI-SIGはPCIe 7.0仕様バージョン0.9(「最終草案」)のリリースを発表しました。最終リリースは2025年に予定されています。[ 124 ]

新しい規格の目標として、以下の主要な点が策定されました。

- ×16構成により、128 GT/sの生ビットレートと最大512 GB/sの双方向通信を実現

- PAM4(4レベルのパルス振幅変調)シグナリングを利用

- チャネルパラメータとリーチに焦点を当てる

- 電力効率の向上

- 低遅延と高信頼性の目標を継続的に達成

- これまでのすべての世代のPCIeテクノロジーとの下位互換性を維持

2025年6月11日、PCI-SIGはPCI Express 7.0の最終仕様のリリースを正式に発表しました。[ 125 ]

PCI-SIGは発表時に、PCIe 7.0がPC市場に登場するのは当分先になるとコメントしました。このインターフェースは当初、クラウドコンピューティング、800ギガビットイーサネット、そして人工知能アプリケーションを対象としています。[ 120 ]

PCIエクスプレス8.0

2025年8月5日、PCI-SIGはPCI Express 8.0の開発を発表しました。この仕様は2028年までにリリースされる予定です。この規格は、以前のバージョンの2倍の速度、つまり256.0GT/sの生ビットレートと、×16構成で最大1TB/sの双方向データ転送を実現します。[ 126 ]

拡張と将来の方向性

一部のベンダーは、PCIe拡張ドロワー内の長距離でのPCIeスイッチング用にアクティブ光ケーブル(AOC)を備えた光ファイバー経由のPCIe製品[ 127 ] [ 128 ] [ 129 ]を提供している。 [ 130 ] [ 103 ]また、追加のソフトウェアが必要になる可能 性のあるより主流の標準( InfiniBandやEthernetなど)を使用するよりも透過的なPCIeブリッジングが望ましい特定のケースでも提供されている。

Thunderboltは、論理PCIeリンクとDisplayPortを組み合わせた汎用高速インターフェースとしてIntelとAppleによって共同開発され、当初は全光ファイバーインターフェースとして意図されていましたが、消費者にとって使いやすい光ファイバー相互接続を実現する初期の困難により、実装のほとんどは銅線システムとなっています。注目すべき例外であるSony VAIO Z VPC-Z2は、光コンポーネントを備えた非標準のUSBポートを使用して外付けPCIeディスプレイアダプターに接続しています。Appleは2011年を通じてThunderbolt採用の主な推進力でしたが、他のいくつかのベンダー[ 131 ]もThunderboltを搭載した新製品やシステムを発表しました。Thunderbolt 3はUSB4標準の基礎を形成しています。

モバイルPCIe仕様(略称:M-PCIe)は、PCI ExpressアーキテクチャをMIPIアライアンスのM-PHY物理層技術上で動作させることを可能にします。既に広く普及しているM-PHYとその低消費電力設計を基盤として、モバイルPCIeはモバイルデバイスでPCI Expressを使用できるようにします。[ 132 ] iPhoneは、 M-PCIeと 統合されたNVMeストレージを活用している例の一つです。

ドラフトプロセス

PCI-SIG仕様には5つの主要なリリース/チェックポイントがあります。[ 133 ]

- ドラフト 0.3 (コンセプト): このリリースには詳細はほとんどありませんが、一般的なアプローチと目標の概要が示されています。

- ドラフト 0.5 (最初のドラフト): このリリースには、アーキテクチャ要件の完全なセットが含まれており、ドラフト 0.3 で設定された目標に完全に対応する必要があります。

- ドラフト0.7(完全ドラフト):このリリースでは、機能要件とメソッドの完全なセットが定義されている必要があり、このリリース以降、仕様に新しい機能を追加することはできません。このドラフトのリリース前に、電気仕様はテストシリコンによって検証されている必要があります。

- ドラフト 0.9 (最終ドラフト): このリリースでは、PCI-SIG メンバー企業が知的財産について内部レビューを実行できます。このドラフト以降、機能の変更は許可されません。

- 1.0 (最終リリース): これは最終的かつ決定的な仕様であり、変更や機能拡張はそれぞれ Errata ドキュメントとエンジニアリング変更通知 (ECN) を通じて行われます。

歴史的に、新しいPCIe仕様をいち早く採用する企業は、通常、ドラフト0.5から設計を開始します。これは、新しい帯域幅定義に基づいてアプリケーションロジックを自信を持って構築でき、新しいプロトコル機能の開発に着手できるからです。しかし、ドラフト0.5の段階では、実際のPCIeプロトコル層の実装に変更が生じる可能性が依然として高いため、これらのブロックを社内で開発する設計者は、外部ソースのインターフェースIPを使用する設計者よりも、作業開始を躊躇する可能性があります。

ハードウェアプロトコルの概要

PCIeリンクは、レーンと呼ばれる専用の単方向シリアル(1ビット)ポイントツーポイント接続のペアを中心に構築されています。これは、すべてのデバイスが同じ双方向の32ビットまたは64ビットパラレルバスを共有するバスベースのシステムである従来のPCI接続とは対照的です。

PCI Expressは、トランザクション層、データリンク層、物理層からなる階層型プロトコルです。データリンク層は、メディアアクセス制御(MAC)サブ層を含むようにさらに細分化されています。物理層は、論理サブ層と電気サブ層にさらに細分化されています。物理論理サブ層には、物理コーディングサブ層(PCS)が含まれます。これらの用語は、IEEE 802ネットワークプロトコルモデルから借用されています。

物理層

| レーン | ピン[ 134 ] | 長さ(mm(インチ)) | ||||

|---|---|---|---|---|---|---|

| ボードコネクタ | コネクタスロット | |||||

| 合計 | 変数 | 合計 | 変数 | 合計 | 変数 | |

| ×1 | 2×18=36 | 2×7=14 | 20.3 (0.8) | 7.2 (0.28) | 25 (1.0) | 7.65 (0.30) |

| ×4 | 2×32=64 | 2×21=42 | 34.3 (1.4) | 21.2 (0.8) | 39 (1.5) | 21.65 (0.85) |

| ×8 | 2×49=98 | 2×38=76 | 51.3 (2.0) | 38.2 (1.5) | 56 (2.2) | 38.65 (1.52) |

| ×16 | 2×82=164 | 2×71=142 | 84.3 (3.3) | 71.2 (2.8) | 89 (3.5) | 71.65 (2.82) |

PCIe物理層(PHY、PCIEPHY、PCI Express PHY、またはPCIe PHY)仕様は、電気的仕様と論理的仕様に対応する2つのサブ層に分かれています。論理サブ層は、MACサブ層とPCSにさらに分割されることもありますが、この区分は正式にはPCIe仕様の一部ではありません。Intelが公開した仕様、PHY Interface for PCI Express(PIPE)[ 135 ]は、MAC/PCS機能分割とこれら2つのサブ層間のインタフェースを定義しています。PIPE仕様では、SerDes (シリアライザ/デシリアライザ)やその他のアナログ回路を含む物理メディアアタッチメント(PMA)層も規定されていますが、SerDesの実装はASICベンダー間で大きく異なるため、PIPEではPCSとPMA間のインタフェースは規定されていません。

電気レベルでは、各レーンは2本の単方向差動ペアで構成され、ネゴシエートされた性能に応じて2.5、5、8、16、または32 Gbit /sで動作します。送信と受信は別々の差動ペアで、レーンごとに合計4本のデータ線があります。

任意の2つのPCIeデバイス間の接続はリンクと呼ばれ、1つ以上のレーンの集合から構築されます。すべてのデバイスは、少なくともシングルレーン(×1)リンクをサポートする必要があります。デバイスはオプションで、最大32レーンで構成されるより広いリンクをサポートできます。[ 136 ] [ 137 ]これにより、以下の2つの点で非常に優れた互換性が実現されます。

- PCIe カードは、少なくとも同じ大きさのスロットであれば物理的に適合し (正常に動作します)、(たとえば、×1 サイズのカードはどのサイズのスロットでも動作します)。

- 大きな物理サイズ (例: ×16) のスロットは、大きな物理スロット サイズに必要なグランド接続が提供される限り、より少ないレーン (例: ×1、×4、×8、または ×12) で電気的に配線できます。

どちらの場合も、PCIeは相互にサポートされる最大のレーン数をネゴシエートします。多くのグラフィックカード、マザーボード、BIOSバージョンは、同一接続で×1、×4、×8、×16の接続をサポートすることが検証されています。

PCIeコネクタの幅は8.8mm、高さは11.25mmで、長さは可変です。コネクタの固定部は長さ11.65mmで、11ピン×2列(合計22ピン)のピン列で構成されています。固定部以外の部分の長さはレーン数に応じて可変です。ピン間隔は1mmで、コネクタに挿入されるカードの厚さは1.6mmです。[ 138 ] [ 139 ]

データ転送

PCIeは、割り込みを含むすべての制御メッセージを、データ用と同じリンクを介して送信します。シリアルプロトコルはブロックされないため、レイテンシは専用の割り込みラインを持つ従来のPCIと同等です。ピンベースの割り込みにおけるIRQ共有の問題と、メッセージシグナル割り込み(MSI)がI/O APICをバイパスしてCPUに直接送信できるという事実を考慮すると、MSIのパフォーマンスは大幅に向上します。[ 140 ]

複数レーンのリンクで送信されるデータはインターリーブされ、連続する各バイトが連続するレーンに送信される。PCIe仕様では、このインターリーブをデータストライピングと呼んでいる。ストライピングは、受信したストライプデータを同期(またはデスキュー)するためにハードウェアをかなり複雑にする必要があるが、リンク上のn番目のバイトのレイテンシを大幅に削減できる。レーンは厳密に同期されていないが、ハードウェアバッファがストライプデータを再調整できるように、2.5/5/8GT/sではレーン間のスキューに20/8/6nsの制限がある。[ 141 ]パディング要件により、ストライピングによってリンク上の小さなデータパケットのレイテンシが必ずしも削減されるわけではない。

他の高データレートシリアル伝送プロトコルと同様、クロックは信号に埋め込まれています。物理レベルでは、PCI Express 2.0 は8b/10b エンコード方式[ 63 ] (ラインコード) を使用して、連続する同一桁 (0 または 1) の文字列の長さが制限されるようにしています。このコーディングは、受信側がビットエッジの位置を見失わないようにするために使用されました。このコーディング方式では、データの 8 ビット (エンコードされていない) ペイロード ビットごとに 10 ビット (エンコードされた) の送信データに置き換えられるため、電気帯域幅に 20% のオーバーヘッドが生じます。使用可能な帯域幅を改善するため、PCI Express バージョン 3.0 では代わりに128b/130bエンコード (1.54% のオーバーヘッド) を使用しています。ラインエンコードは、データ ストリーム内の同一桁の文字列の連続長を制限し、クロック回復を介して受信側が送信側と同期を保つようにします。

データストリーム中の0ビットと1ビットの望ましいバランス(ひいてはスペクトル密度)は、フィードバックトポロジーにおいて、既知の2進多項式を「スクランブラー」としてデータストリームに排他的論理和(XOR)することで実現されます。スクランブル多項式は既知であるため、XORを再度適用することでデータを復元できます。スクランブルとデスクランブルの両方のステップはハードウェアで実行されます。

PCIeにおけるデュアルシンプレックスとは、各PCIeレーンに2つのシンプレックスチャネルがあることを意味します。シンプレックスとは、通信が片方向のみ可能であることを意味します。2つのシンプレックスチャネルを持つことで、双方向通信が可能になります。各チャネルには1つの差動ペアが使用されます。[ 142 ] [ 1 ] [ 143 ]

データリンク層

データ リンク層は、PCIe リンクに対して 3 つの重要なサービスを実行します。

- トランザクション層によって生成されたトランザクション層パケット(TLP)を順序付ける。

- 確認応答プロトコル(ACKおよびNAKシグナリング)を介して2つのエンドポイント間のTLPの信頼性の高い配信を確保し、確認応答のないTLPや不良TLPの再生を明示的に要求する。

- フロー制御クレジットの初期化と管理

送信側では、データリンク層が送信TLPごとに増分するシーケンス番号を生成します。このシーケンス番号は送信TLPごとに固有の識別タグとして機能し、送信TLPのヘッダーに挿入されます。また、送信TLPの末尾には32ビットの巡回冗長検査コード(この文脈ではリンクCRCまたはLCRCと呼ばれます)が付加されます。

受信側では、受信したTLPのLCRCとシーケンス番号の両方がリンク層で検証されます。LCRCチェックが失敗(データエラーを示す)した場合、またはシーケンス番号が範囲外(最後に受信した有効なTLPと連続していない)の場合、不正なTLPと、それ以降に受信したすべてのTLPは無効とみなされ、破棄されます。受信側は、無効なTLPのシーケンス番号を記載した否定応答メッセージ(NAK)を送信し、そのシーケンス番号以降のすべてのTLPの再送を要求します。受信したTLPがLCRCチェックに合格し、正しいシーケンス番号を持つ場合、有効とみなされます。リンク受信側は、シーケンス番号(最後に受信した有効なTLPを追跡する番号)をインクリメントし、有効なTLPを受信側のトランザクション層に転送します。TLPが正常に受信されたことを示すACKメッセージがリモート送信側に送信され(拡張により、それ以前のシーケンス番号を持つすべてのTLPも受信されたことが示されます)、

送信側がNAKメッセージを受信した場合、またはタイムアウト期間が経過するまでに確認応答(NAKまたはACK)を受信しなかった場合、送信側は肯定応答(ACK)が返されないすべてのTLPを再送信する必要があります。デバイスまたは伝送媒体に継続的な障害が発生しない限り、リンク層はトランザクション層への信頼性の高い接続を提供します。これは、伝送プロトコルが信頼性の低い媒体を介したTLPの配信を保証するためです。

データリンク層は、トランザクション層によって生成されたTLPの送受信に加えて、データリンク層パケット(DLLP)も生成および消費します。ACK信号とNAK信号は、一部の電源管理メッセージやフロー制御クレジット情報(トランザクション層に代わって)と同様に、DLLPを介して通信されます。

実際には、リンク上の未確認TLPの数は、送信側のリプレイバッファのサイズ(リモート受信側が確認応答するまで、送信されたすべてのTLPのコピーを保存する必要がある)と、受信側から送信側に発行されるフロー制御クレジットという2つの要因によって制限されます。PCI Expressでは、リンクがPCIConfig TLPとメッセージTLPの送信を可能にするために、すべての受信側が最低限の数のクレジットを発行することが求められます。

トランザクション層

PCI Express は分割トランザクション (要求と応答が時間で分離されたトランザクション) を実装し、ターゲット デバイスが応答のデータを収集している間にリンクが他のトラフィックを伝送できるようにします。

PCI Express はクレジットベースのフロー制御を使用します。この方式では、デバイスはトランザクション層で受信したバッファごとに初期クレジット量を通知します。リンクの反対側のデバイスは、このデバイスにトランザクションを送信する際、各 TLP が自身のアカウントから消費するクレジット数をカウントします。送信デバイスは、消費したクレジット数がクレジット制限を超えない場合にのみ、TLP を送信できます。受信デバイスはバッファからの TLP の処理を完了すると、送信デバイスにクレジットの返却を通知し、返却されたクレジット量だけクレジット制限が増加します。クレジットカウンタはモジュラカウンタであり、消費クレジットとクレジット制限の比較にはモジュラ演算が必要です。この方式の利点は (待機状態やハンドシェイクベースの転送プロトコルなどの他の方法と比較して)、クレジット制限に達しない限り、クレジット返却の遅延がパフォーマンスに影響を与えないことです。この仮定は、各デバイスが適切なバッファサイズで設計されている場合に一般的に満たされます。

PCIe 1.xは、レーンごとに双方向で250MB/秒のデータレートをサポートするとよく言われます。この数値は、物理的な信号レート(2.5 ギガボー)をエンコードオーバーヘッド(1バイトあたり10ビット)で割った値です。つまり、16レーン(×16)のPCIeカードは、理論上、双方向で16×250MB/秒 = 4GB/秒の速度を実現できることになります。これはデータバイト数の観点からは正しいのですが、より意味のある計算は、トラフィックのプロファイル、つまり高レベル(ソフトウェア)アプリケーションと中間プロトコルレベルの関数によって決まる、使用可能なデータペイロードレートに基づいています。

他の高データレートのシリアル相互接続システムと同様に、PCIe には、追加の転送堅牢性 (CRC および確認応答) によるプロトコルおよび処理のオーバーヘッドがあります。 長時間の連続した単方向転送 (高性能ストレージ コントローラで一般的なものなど) は、PCIe の生の (レーン) データ レートの 95% 以上に近づくことがあります。 これらの転送は、レーン数の増加 (×2、×4 など) から最大の恩恵を受けます。 しかし、より一般的なアプリケーション ( USBまたはEthernetコントローラなど) では、トラフィック プロファイルは、頻繁に強制確認応答を伴う短いデータ パケットとして特徴付けられます。[ 144 ]このタイプのトラフィックは、パケット解析によるオーバーヘッドと強制割り込み (デバイスのホスト インターフェイスまたは PC の CPU のいずれか) により、リンクの効率を低下させます。 同じプリント基板に接続されたデバイス用のプロトコルであるため、長距離通信用のプロトコルほどの伝送エラーに対する許容度は必要とせず、そのため、この効率の低下は PCIe に特有のものではありません。

リンクの効率

ネットワークのような通信リンクでは、帯域幅の一部はプロトコルのオーバーヘッドによって消費されます。[ 145 ]

例えば、PCIe 1.xレーンは、物理層上で250 MB/s(片方向)のデータレートを提供します。これは、2.5 GT/sのビットレートに8b/10bラインコードの効率を乗じた結果です(比較表を参照)。これはペイロード帯域幅ではなく、物理層帯域幅です。PCIeレーンは、完全な機能を実現するために、追加情報を伝送する必要があります。[ 145 ]

| 層 | 物理 | データリンク層 | 取引 | データリンク層 | 物理 | ||

|---|---|---|---|---|---|---|---|

| データ | 始める | 順序 | ヘッダ | ペイロード | ECRC | LCRC | 終わり |

| サイズ(バイト) | 1 | 2 | 12または16 | 0から4096 | 4(オプション) | 4 | 1 |

Gen2 のオーバーヘッドは、トランザクションごとに 20、24、または 28 バイトになります。

| 層 | 物理 | データリンク層 | トランザクション層 | データリンク層 | ||

|---|---|---|---|---|---|---|

| データ | 始める | 順序 | ヘッダ | ペイロード | ECRC | LCRC |

| サイズ(バイト) | 4 | 2 | 12または16 | 0から4096 | 4(オプション) | 4 |

Gen3 のオーバーヘッドは、トランザクションごとに 22、26、または 30 バイトになります。

パケット効率 = ペイロード/ペイロード + オーバーヘッド 128バイトのペイロードでは86%、1024バイトのペイロードでは98%です。レジスタ設定(4バイト)のような小さなアクセスでは、効率は16%まで低下します。とはいえ、ほとんどのPCIe構成レジスタはCPUの制御レジスタにマッピングされたDMA領域に配置されており、バスアクセスを必要としません。

最大ペイロードサイズ(MPS)は、チェーン内のデバイスの最小値に基づいて、すべてのデバイスに設定されます。あるデバイスのMPSが128バイトの場合、ツリー内のすべてのデバイスのMPSを128バイトに設定する必要があります。この場合、バスの書き込み効率は最大86%になります。[ 145 ] : 3

アプリケーション

PCI Express は、消費者、サーバー、産業用アプリケーションにおいて、マザーボード レベルの相互接続 (マザーボードに取り付けられた周辺機器をリンク)、パッシブ バックプレーン相互接続、およびアドイン ボードの 拡張カードインターフェイスとして動作します。

2012年現在、コンシューマー向けノートパソコンやデスクトップパソコンからエンタープライズサーバーに至るまで、ほぼすべての最新PCにおいて、PCIeバスはマザーボードレベルの主要な相互接続として機能し、ホストシステムプロセッサと内蔵周辺機器(表面実装IC)およびアドオン周辺機器(拡張カード)の両方を接続しています。これらのシステムの中には、PCIeバスが1つ以上のレガシーPCIバスと共存し、多数のレガシーPCI周辺機器との下位互換性を確保しているものもあります。

2013年現在、新しいシステムのグラフィックカードのデフォルトインターフェースはAGPに代わりPCI Expressになりました。 2010年以降にAMD(ATI)とNvidiaがリリースしたグラフィックカードのほぼすべてのモデルはPCI Expressを採用しています。AMD、Nvidia、Intelは、最大4つのPCIe x16スロットをサポートするマザーボードチップセットをリリースしており、3基または4基のGPUカード構成が可能です。

外付けGPU

理論上、外付けPCIeは、ノートパソコンにPCIeデスクトップビデオカード(専用の外付けハウジングに収納され、電源と冷却機能を備えているもの)を接続することで、デスクトップ並みのグラフィックス性能をノートパソコンに提供できます。これは、ExpressCardまたはThunderboltインターフェースで実現可能です。ExpressCardインターフェースは5Gbit/s(スループット0.5GB/s)のビットレートを提供するのに対し、Thunderboltインターフェースは最大40Gbit/s(スループット5GB/s)のビットレートを提供します。

2006年、Nvidiaはプロフェッショナル市場向けの高度なグラフィックアプリケーションに使用できるQuadro Plex外付けPCIe GPUファミリーを開発しました。 [ 146 ]これらのビデオカードは、ホスト側カードにPCI Express ×8または×16スロットを必要とし、8つのPCIeレーンを備えたVHDCIを介してPlexに接続します。[ 147 ]

2008年、AMDはPCIe×8信号伝送に対応した独自のケーブルシステムに基づくATI XGPテクノロジーを発表しました。 [ 148 ]このコネクタは、富士通AmiloとAcer Ferrari Oneノートパソコンに搭載されています。その後まもなく、富士通はXGP用のAMILO GraphicBoosterエンクロージャを発売しました。[ 149 ] 2010年頃、AcerはXGP用のDynavividグラフィックドックを発売しました。[ 150 ]

2010年には、PCI ExpressCardスロットを介してノートパソコンやデスクトップパソコンに接続できる外付けカードハブが登場しました。これらのハブはフルサイズのグラフィックカードに対応しています。例としては、MSI GUS [ 151 ] 、 Village InstrumentのViDock [ 152 ] 、 Asus XG Station、Bplus PE4H V3.2アダプタ[ 153 ]、そしてより自作的なDIYデバイスなどが挙げられます。[ 154 ]しかし、このようなソリューションは、ノートパソコンのPCIeスロットのサイズ(多くの場合×1のみ)とバージョンによって制限されます。

Intel Thunderboltインターフェースは、PCIeカードを外部接続するための新しい選択肢を提供しました。Magmaは、最大3枚のPCIeカード(×8が2枚、×4が1枚)を搭載できるExpressBox 3Tをリリースしました。[ 155 ] MSIもビデオカード専用のPCIeシャーシThunderbolt GUS IIをリリースしました。[ 156 ] SonnetのEcho Express [ 157 ]やmLogicのmLinkなどの他の製品も、より小型のフォームファクタのThunderbolt PCIeシャーシです。[ 158 ]

2017年には、フルレングスのPCIe×16インターフェースを備えたRazer Coreなど、より機能豊富な外付けカードハブが導入されました。[ 159 ]

ストレージデバイス

PCI Express プロトコルは、メモリ カードやソリッド ステート ドライブ(SSD) などのフラッシュ メモリデバイスへのデータ インターフェイスとして使用できます。

XQDカードは、CompactFlash Associationによって開発されたPCI Expressを利用したメモリカードフォーマットであり、最大1GB/秒の転送速度を実現します。[ 160 ]

多くの高性能エンタープライズクラスSSDは、PCI Express RAIDコントローラカードとして設計されています。NVMeが標準化される前は、これらのカードの多くはオペレーティングシステムとの通信に独自のインターフェースとカスタムドライバを使用していました。これらのカードは、シリアルATAやSASドライブと比較して、はるかに高い転送速度(1GB/秒以上)とIOPS(1秒あたり100万I/O操作以上)を実現していました。[ 161 ] [ 162 ]例えば、2011年にOCZとMarvellは、PCI Express 3.0 ×16スロット用のネイティブPCI Expressソリッドステートドライブコントローラを共同開発しました。このコントローラは、最大容量12TB、シーケンシャル転送速度7.2GB/秒、ランダム転送速度最大252万IOPSを実現していました。[ 163 ]

SATA Expressは、SATA互換ポートを介してSSDを接続するためのインターフェースであり、接続されたストレージデバイスへの純粋なPCI Express接続として複数のPCI Expressレーンをオプションで提供します。[ 164 ] M.2は、最大4つのPCI Expressレーンを使用できる、内部に取り付けられたコンピュータ拡張カードと関連コネクタの仕様です。[ 165 ]

PCI Expressストレージデバイスは、後方互換性を確保するためのAHCI論理インターフェースと、デバイス内部の並列処理を利用することで実現される、はるかに高速なI/O操作を実現するNVM Express論理インターフェースの両方を実装できます。エンタープライズクラスのSSDは、PCI Express経由でSCSIを実装することもできます。[ 166 ]

クラスタ相互接続

特定のデータセンターアプリケーション(大規模コンピュータクラスタなど)では、銅線ケーブル配線に固有の距離制限のため、光ファイバー相互接続を使用する必要があります。通常、これらのアプリケーションにはイーサネットやファイバーチャネルなどのネットワーク指向の標準で十分ですが、ルーティング可能なプロトコルによって生じるオーバーヘッドが望ましくない場合があり、 InfiniBand、RapidIO、NUMAlinkなどの低レベルの相互接続が必要になります。PCIeやHyperTransportなどのローカルバス標準は、原理的にはこの目的で使用できますが、[ 167 ] 2015年時点では、 Dolphin ICSやTTTech Autoなどのニッチベンダーからのみソリューションが提供されています。

競合するプロトコル

PCIe 1.0は当初、 PCI-X 2.0と競合していました。両仕様とも2003年に承認され、ほぼ同じ最大帯域幅(約4GB/秒)を提供していました。しかし、2005年までにPCIeが主流の技術となりました。

高帯域幅シリアルアーキテクチャに基づく他の通信規格には、InfiniBand、RapidIO、HyperTransport、Intel QuickPath Interconnect、Mobile Industry Processor Interface(MIPI)、NVLinkなどがあります。これらの規格の違いは、柔軟性と拡張性と、レイテンシとオーバーヘッドとのトレードオフに基づいています。例えば、InfiniBandのようにシステムをホットプラグ可能にするには(PCI Expressとは異なり)、ソフトウェアがネットワークトポロジの変更を追跡する必要があります。

もう1つの例としては、レイテンシを低減するためにパケットを短くすることが挙げられます(バスをメモリインターフェースとして動作させる必要がある場合など)。パケットが小さくなると、パケットヘッダーがパケットのより大きな割合を占めるため、実効帯域幅が減少します。この目的のために設計されたバスプロトコルの例としては、RapidIOやHyperTransportなどがあります。

PCI Expressはその中間に位置し、デバイス相互接続やルーティングされたネットワークプロトコルではなく、システム相互接続(ローカルバス)として設計されています。さらに、ソフトウェア透過性という設計目標によりプロトコルに制約が生じ、レイテンシが若干増加します。

PCIe 4.0の実装の遅れにより、 Gen-Zコンソーシアム、CCIXの取り組み、オープンなコヒーレントアクセラレータプロセッサインターフェース(CAPI)がすべて2016年末までに発表されました。[ 168 ]

2019年3月11日、インテルはPCI Express 5.0物理層インフラストラクチャをベースとした新しい相互接続バス、Compute Express Link (CXL)を発表しました。CXL仕様の初期推進企業には、アリババ、シスコ、Dell EMC、Facebook、Google、HPE、Huawei、インテル、Microsoftなどが含まれていました。[ 169 ]

インテグレーターリスト

PCI-SIGインテグレーターリストには、PCI-SIG加盟企業が製造し、コンプライアンステストに合格した製品が掲載されています。リストには、スイッチ、ブリッジ、NIC、SSDなどが含まれます。[ 170 ]

参照

注記

- ^スイッチは 1 つのエンドポイントから複数のエンドポイントを作成し、複数のデバイスで共有することができます。

- ^ USB 3.0ポートはPCI Expressバスが供給できる以上の電力を必要とするため、カードにシリアルATA電源コネクタが搭載されています。多くの場合、 4ピンのMolex電源コネクタが使用されます。

参考文献

- ^ a b IBM Power 770および780の技術概要と導入。IBM Redbooks。2013年6月6日。ISBN 978-0-7384-5121-3。

- ^ Mayhew, D.; Krishnan, V. (2003年8月). 「PCI Expressと高度なスイッチング:次世代インターコネクト構築への進化の道」.第11回高性能インターコネクトシンポジウム, 2003. Proceedings . pp. 21– 29. doi : 10.1109/CONECT.2003.1231473 . ISBN 0-7695-2012-X. S2CID 7456382 .

- ^ 「PCI Expressの定義」。PCMag 。

- ^ Zhang, Yanmin; Nguyen, T Long (2007年6月). 「カーネルでPCI Expressの高度なエラー報告を有効にする」(PDF) . Proceedings of the Linux Symposium . Fedoraプロジェクト.オリジナル(PDF)から2016年3月10日時点のアーカイブ。 2012年5月8日閲覧。

- ^ https://www.hyperstone.comフラッシュメモリフォームファクタ – 信頼性の高いフラッシュストレージの基礎、2018年4月19日閲覧

- ^ a b c Ravi Budruk (2007年8月21日). 「PCI Expressの基礎」 . PCI-SIG . 2014年7月15日時点のオリジナル(PDF)からアーカイブ。 2014年7月15日閲覧。

- ^ 「PCIeスロットとは何か、そしてその用途とは?」 PCガイド101、2021年5月18日。 2021年6月21日閲覧。

- ^ Wilson, Tracy V. (2005年8月17日). 「PCI Expressの仕組み」How Stuff Works . 2009年12月3日時点のオリジナルよりアーカイブ。2009年12月7日閲覧。

- ^「4.2.4.9. リンク幅とレーンシーケンスネゴシエーション」、PCI Express基本仕様、リビジョン2.1、2009年3月4日

- ^ a b c「PCI Expressアーキテクチャに関するよくある質問」。PCI-SIG。2008年11月13日時点のオリジナルよりアーカイブ。 2008年11月23日閲覧。

- ^ 「PCI Expressバス」。インターフェースバス。 2007年12月8日時点のオリジナルよりアーカイブ。2010年6月12日閲覧。

- ^ PCIe 5.0 までのPCIe ベース仕様では 32 レーンとして定義されていますが、 PCIe カード電気機械仕様にはカード標準がなく、そのレーン数は実装されていません。

- ^ 「PCI Express – PCI Express規格の概要」開発者ゾーン、ナショナルインスツルメンツ、2009年8月13日。2010年1月5日時点のオリジナルよりアーカイブ。 2009年12月7日閲覧。

- ^ Qazi, Atif. 「PCIeスロットとは?」 PC Gear Lab . 2020年8月3日時点のオリジナルよりアーカイブ。 2020年4月8日閲覧。

- ^ 「新しいPCIeフォームファクターによりPCIe SSDの普及が促進される」 NVM Express、2012年6月12日。2015年9月6日時点のオリジナルよりアーカイブ。

- ^ 「Memblaze PBlaze4 AIC NVMe SSDレビュー」 . StorageReview . 2015年12月21日.

- ^ a b PCI Expressカード電気機械仕様リビジョン4.0、バージョン0.9=。2018年11月。(PCIe_CEM_SPEC_R4_V9_12072018_NCB.pdf)

- ^ Fulton, Kane (2015年7月20日). 「ゲームの未来を形作る19のグラフィックカード」 . TechRadar .

- ^ Leadbetter, Richard (2020年9月16日). 「Nvidia GeForce RTX 3080レビュー:次のレベルへようこそ」 . Eurogamer .

- ^ Discuss、btarunr (2023年1月6日). 「ASUS × Noctua RTX 4080グラフィックスカードは5スロット厚、ハンズオンで検証」 . TechPowerUp . 2024年9月19日閲覧。

- ^ 「Sapphire Radeon RX 5700 XT Pulseレビュー | bit-tech.net」 . bit-tech.net . 2019年8月26日閲覧。

- ^ “AMD Radeon™ RX 5700 XT 8GB GDDR6 THICC II – RX-57XT8DFD6” . xfxforce.com . 2019年9月1日時点のオリジナルよりアーカイブ。2019年8月25日閲覧。

- ^ 「ROG Strix GeForce RTX 3080 OC Edition 10GB GDDR6X | グラフィックカード」。rog.asus.com 。

- ^ 「PCIカードのA面、B面構成とは何ですか?」よくある質問. Adex Electronics. 1998年. 2011年11月2日時点のオリジナルよりアーカイブ。2011年10月24日閲覧。

- ^ a b PCI Expressカード電気機械仕様改訂2.0

- ^ 「PCI Express カード電気機械仕様リビジョン 4.0、バージョン 1.0 (クリーン)」。

- ^ 「CLKREQ付きL1 PMサブステート、リビジョン1.0a」(PDF) . PCI-SIG. 2018年12月4日時点のオリジナル(PDF)からアーカイブ。 2018年11月8日閲覧。

- ^ 「PWRBRK信号ECNによる緊急電力削減メカニズム」(PDF) PCI-SIG。2018年11月9日時点のオリジナル(PDF)からアーカイブ。 2018年11月8日閲覧。

- ^ 「PCIeケーブルはどこに接続すればよいのか?」 2022年1月16日。 2022年6月10日閲覧。

- ^ PCI Express カード電気機械仕様改訂 1.1

- ^ Schoenborn, Zale (2004)、PCI Expressアーキテクチャのボード設計ガイドライン(PDF)、PCI-SIG、pp. 19– 21、2016年3月27日時点のオリジナルよりアーカイブ(PDF)

- ^ PCI Express 基本仕様、リビジョン 1.1、332ページ

- ^ a b「Mini-Fit® PCI Express®* ワイヤ対ボードコネクタシステム」(PDF) 。 2020年12月4日閲覧。

- ^ PCI Express ×16 グラフィックス 150W-ATX 仕様改訂 1.0

- ^ PCI Express 225 W/300 W 高出力カード電気機械仕様改訂 1.0

- ^ PCI Express カード電気機械仕様改訂 3.0

- ^ Yun Ling (2008年5月16日). 「PCIe Electromechanical Updates」 . 2015年11月5日時点のオリジナルよりアーカイブ。2015年11月7日閲覧。

- ^ 「12VHPWRサイドバンドの割り当てと要件 - PCIe 5.x ECN」。PCI SIG。2022年5月12日。

- ^ 「12V-2x6コネクタのPCIe Base 6.0へのアップデート - PCIe 6.x ECN」 . PCI SIG. 2023年8月31日.

このECNは、新しい12V-2x6コネクタのコネクタタイプエンコーディングを定義します。CEM 5.1で定義されたこのコネクタは、12VHPWRコネクタに代わるものです。

- ^ Walllossek, Igor (2023年7月3日). 「Rest in Peace 12VHPWR Connector - Welcome 12V-2×6 Connector, important modifications and PCIe Base 6 | Exclusive」 . igor'sLAB . 2025年2月9日閲覧。

- ^ 「12VHPWRと12V-2x6の比較」 Corsair . 2025年2月9日閲覧。

- ^ Buildzoid (2025年2月11日). 「Nvidiaが12VHPWRコネクタをさらに悪化させた経緯」 .アクチュアリー・ハードコア・オーバークロック. 2025年9月9日閲覧– YouTube経由.

- ^ Nilange, Manisha. (T1S02 & T1S08) PCIe CEMの最新情報. PCI-SIG開発者会議2023.

- ^ 「PCI-Express(PCIe)アドインカードコネクタ(推奨)」。ATXバージョン3マルチレールデスクトッププラットフォーム電源設計ガイド、リビジョン2.1a。Intel Corporation 。 2023年11月1日。61 ~ 65ページ。Intel 文書番号336521-2.1a。2025年2月14日時点のオリジナルからのアーカイブ(PDF) 。 2025年9月9日閲覧。

- ^ PCI Expressカード電気機械仕様改訂5.1、バージョン1.0、2023年3月30日 – 10. PCI Express 48VHPWR補助電源コネクタの定義

- ^

- ^ 「次世代 SSD を高速化するインターフェース、M.2 を理解する」 2015 年 2 月 8 日。

- ^ "MP1: Mini PCI Express / PCI Express アダプター" . hwtools.net . 2014年7月18日. 2014年10月3日時点のオリジナルよりアーカイブ。 2014年9月28日閲覧。

- ^ IT Essentials Companion Guide v8 . Cisco Press. 2023年7月9日. ISBN 978-0-13-816625-0。

- ^モバイルコンピューティングの導入と管理:CompTIA Mobility+認定資格取得のための実践的なスキルとそれ以降のスキル. John Wiley & Sons. 2015年2月24日. ISBN 978-1-118-82461-0。

- ^ 「mSATA FAQ: 基礎入門」。ノートパソコンのレビュー。2012年2月12日時点のオリジナルよりアーカイブ。

- ^ "Eee PC Research" . ivc (wiki). 2010年3月30日時点のオリジナルよりアーカイブ。 2009年10月26日閲覧。

- ^ 「デスクトップボードのソリッドステートドライブ(SSD)の互換性」 Intel . 2016年1月2日時点のオリジナルよりアーカイブ。

- ^ 「M.2カードの違いを見分ける方法 | Dell US」 www.dell.com 2020年3月24日閲覧。

- ^ 「PCI Express 外部ケーブル接続 1.0 仕様」。2007年2月10日時点のオリジナルよりアーカイブ。2007年2月9日閲覧。

- ^ 「PCI-SIGがPCI Express外部ケーブル仕様を完成」 PCI SIG、2007年2月7日。2013年11月26日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ a b「OCuLinkコネクタとケーブルが新しいPCIe規格をサポート」 www.connectortips.com 。 2017年3月13日時点のオリジナルよりアーカイブ。

- ^ Mokosiy, Vitaliy (2020年10月9日). 「用語の解説:M.2、NVMe、USB-C、SAS、PCIe、U.2、OCuLink」 . Medium . 2021年3月26日閲覧。

- ^ 「Supermicro Universal I/O (UIO) ソリューション」 Supermicro.com。2014年3月24日時点のオリジナルよりアーカイブ。 2014年3月24日閲覧。

- ^ 「M-PCIeテストの準備」、PCボード設計、EDN

- ^ a b「PCI SIG、M-PCIe oculinkと第4世代PCIeについて議論」、The Register、英国、2013年9月13日、2017年6月29日時点のオリジナルよりアーカイブ

- ^ 「PCI Express 4.0 よくある質問」 . pcisig.com . PCI-SIG. 2014年5月18日時点のオリジナルよりアーカイブ。 2014年5月18日閲覧。

- ^ a b c「PCI Express 3.0 よくある質問」 . pcisig.com . PCI-SIG. 2014年2月1日時点のオリジナルよりアーカイブ。 2014年5月1日閲覧。

- ^ "PCI-Express-Schnittstelle: PCIe 7.0 および Die Basis für optische Verbindungen stehen、PCIe 8.0 folgt" . 2025 年 6 月 11 日。

- ^ 「GT/sとは一体何を意味するのか?」 TM World . 2012年8月14日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ "Deliverable 12.2" . SE : Eiscat. 2010年8月17日時点のオリジナルよりアーカイブ。2012年12月7日閲覧。

- ^ PCI SIG、2008年7月6日時点のオリジナルよりアーカイブ

- ^ 「PCI Express Base 2.0仕様発表」(PDF) (プレスリリース). PCI-SIG . 2007年1月15日.オリジナル(PDF)から2007年3月4日時点のアーカイブ。 2007年2月9日閲覧。— このプレスリリースでは、総帯域幅という用語は着信帯域幅と発信帯域幅の合計を指します。この用語を使用すると、全二重 100BASE-TX の総帯域幅は 200 Mbit/s になります 。

- ^ Smith, Tony (2006年10月11日). 「PCI Express 2.0 最終ドラフト仕様公開」 . The Register . 2007年1月29日時点のオリジナルよりアーカイブ。2007年2月9日閲覧。

- ^ Key, Gary; Fink, Wesley (2007年5月21日). 「Intel P35: Intelのメインストリームチップセットが成長」 . AnandTech . 2007年5月23日時点のオリジナルよりアーカイブ。 2007年5月21日閲覧。

- ^ Huynh, Anh (2007年2月8日). 「NVIDIA "MCP72" Details Unveiled」 . AnandTech . 2007年2月10日時点のオリジナルよりアーカイブ。2007年2月9日閲覧。

- ^ 「Intel P35 Expressチップセット製品概要」(PDF)。Intel。2007年9月26日時点のオリジナルよりアーカイブ(PDF) 。 2007年9月5日閲覧。

- ^ Hachman, Mark (2009年8月5日). 「PCI Express 3.0仕様、2010年に延期」 . PC Mag. 2014年1月7日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ 「PCI Express 3.0 帯域幅: 8.0 ギガ転送/秒」 ExtremeTech、2007年8月9日。2007年10月24日時点のオリジナルよりアーカイブ。 2007年9月5日閲覧。

- ^ 「PCI Special Interest GroupがPCI Express 3.0規格を公開」。X bit labs。2010年11月18日。2010年11月21日時点のオリジナルよりアーカイブ。 2010年11月18日閲覧。

- ^ 「PCIe 3.1および4.0の仕様が公開された」 eteknix.com 2013年7月。2016年2月1日時点のオリジナルよりアーカイブ。

- ^ “Trick or Treat… PCI Express 3.1 Released!” synopsys.com . 2015年3月23日時点のオリジナルよりアーカイブ。

- ^ 「PCI Express 4.0、16 GT/sへの進化、PCI Express 3.0技術の2倍のスループット」(プレスリリース)。PCI-SIG。2011年11月29日。 2012年12月23日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ 「よくある質問 | PCI-SIG」pcisig.com . 2016年10月20日時点のオリジナルよりアーカイブ。

- ^ 「PCIe 4.0 Heads to Fab, 5.0 to Lab」 EE Times 2016年6月26日。2016年8月28日時点のオリジナルよりアーカイブ。 2016年8月27日閲覧。

- ^ 「Mellanox 、次世代の 100G InfiniBand および Ethernet スマート相互接続アダプタ ConnectX-5 を発表 | NVIDIA」www.mellanox.com。

- ^ 「Mellanox 、記録的なパフォーマンスとスケーラビリティを実現する 200Gb/s HDR InfiniBand ソリューションを発表 | NVIDIA」www.mellanox.com。

- ^ "IDF: PCIe 4.0 は残り、PCIe 5.0 は任意に" . Heise Online (ドイツ語)。 2016 年 8 月 18 日。2016年 8 月 19 日のオリジナルからアーカイブ。2016 年8 月 18 日に取得。

- ^ 「Brian Thompto、コグニティブ時代のPOWER9プロセッサ」(PDF)。

- ^ 2016 IEEE Hot Chips 28シンポジウム(HCS)、2016年8月21~23日

- ^ a b Born, Eric (2017年6月8日). 「PCIe 4.0仕様がついに発表、16 GT/sを実現」テックレポート.オリジナルより2017年6月8日時点のアーカイブ。 2017年6月8日閲覧。

- ^ 「IBM、AI向け最先端サーバーを発表」 www-03.ibm.com 2017年12月5日。2017年12月8日時点のオリジナルよりアーカイブ。

- ^ 「IBM Power System AC922(8335-GTG)サーバーは、画期的なAI、HPDA、HPCの高速化パフォーマンスを活用し、より迅速な洞察獲得を実現します」 www.ibm.com 2017年12月5日。 2024年6月27日時点のオリジナルよりアーカイブ。 2025年4月25日閲覧。

- ^ 「NETINT、PCIe 4.0をサポートするCodensityを発表 – NETINT Technologies」 . NETINT Technologies . 2018年7月17日. 2018年9月29日時点のオリジナルよりアーカイブ。 2018年9月28日閲覧。

- ^ Mujtaba, Hassan (2019年1月9日). 「Zen 2ベースのAMD Ryzen 3000シリーズCPU、2019年半ばに発売」 .

- ^ Alcorn, Paul (2019年6月3日). 「AMD、旧ソケットAM4マザーボードのPCIe 4.0サポートを廃止、その理由はここに」 . Tom's Hardware . 2019年6月10日時点のオリジナルよりアーカイブ。 2019年6月10日閲覧。

- ^ Alcorn, Paul (2019年1月10日). 「PCIe 4.0がすべてのAMD Socket AM4マザーボードに搭載される可能性(更新)」 . Tom's Hardware . 2019年6月10日時点のオリジナルよりアーカイブ。 2019年6月10日閲覧。

- ^ Cutress, Dr. Ian (2020年8月13日). 「Tiger LakeのIOと電力」 . Anandtech . 2020年10月2日時点のオリジナルよりアーカイブ。

- ^ 「1,2,3,4,5... PCIe 5.0が正式に発表されました | synopsys.com」www.synopsys.com . 2017年6月7日閲覧。

- ^ 「PLDA、XpressRICH5™ PCIe 5.0コントローラIPの提供開始を発表 | PLDA.com」 www.plda.com . 2018年6月28日閲覧。

- ^ 「XpressRICH5 for ASIC | PLDA.com」www.plda.com . 2018年6月28日閲覧。

- ^ 「2年以内に帯域幅を2倍に:PCI Express®基本仕様リビジョン5.0、バージョン0.9が会員向けに公開」 pcisig.com . 2018年12月12日閲覧。

- ^ 「PCIe 5.0、プライムタイム対応完了」 tomshardware.com 、 2019年1月17日。 2019年1月18日閲覧。

- ^ 「PCI-SIG®、新しいPCI Express® 5.0仕様で32GT/sを達成」 www.businesswire.com 2019年5月29日

- ^ "PCI-Express 5.0: 中国の最新のコントローラー" . PC ゲーム ハードウェア。 2019年11月18日。

- ^ 「IBMのPOWER10プロセッサー、Hot Chips 32、2020年8月16~18日」(PDF)。

- ^ Power E1080 Enterprise サーバーは、ハイブリッドクラウドでコア運用アプリケーションと AI アプリケーションを安全かつ効率的に拡張するのに役立つ独自のアーキテクチャを備えたプラットフォームを提供します。IBM ヨーロッパハードウェア発表 ZG21-0059

- ^ a b IBM Power E1080 技術概要と導入

- ^ 「Intel、第12世代Intel Coreを発表、世界最高のゲーミングを提供」 Intel.com、2021年12月31日。 2022年2月16日閲覧。

- ^ 「NVIDIA、次世代の加速コンピューティングである Hopper アーキテクチャを発表」。

- ^ 「AMD、COMPUTEX 2022で業界をリードするゲーミング、商用、メインストリームPCテクノロジーを展示」 AMD.com 2022年5月23日閲覧。

- ^ 「第4世代AMD EPYC™プロセッサーアーキテクチャ」 AMD.com 2022年11月12日閲覧。

- ^ a b「PCI-SIG®、64 GT/sを実現するPCI Express® 6.0仕様を発表」 www.businesswire.com 2019年6月18日

- ^ライアン・スミス「PCI Express帯域幅が再び倍増:PCIe 6.0発表、仕様は2021年に実装へ」 www.anandtech.com 。 2019年6月18日時点のオリジナルよりアーカイブ。

- ^ 「PCI Express 6.0、来年の最終版に先立ちバージョン0.5に到達 – Phoronix」www.phoronix.com。

- ^ Shilov, Anton (2020年11月4日). 「PCIe 6.0仕様がマイルストーンに到達:完全なドラフト版が完成」 . Tom's Hardware .

- ^ Yanes, Al. 「PCIe® 6.0仕様、バージョン0.9:最終リリースに一歩近づく | PCI-SIG」pcisig.com . 2021年10月6日閲覧。

- ^ 「PCI-SIG®、ビッグデータアプリケーションを強化する記録的なパフォーマンスを実現するPCIe® 6.0仕様を発表」 Business Wire、2022年1月11日。 2022年2月16日閲覧。

- ^ 「PCI Express仕様の進化:第6世代、30年を経てもなお健在」 PCI-Sig、2022年1月11日。 2022年2月16日閲覧。

- ^ Debendra Das Sharma (2020年6月8日). 「PCIe 6.0仕様:将来のI/Oニーズに対応するインターコネクト」 . PCI-SIG. p. 8. 2021年10月30日時点のオリジナルよりアーカイブ。

- ^ 「PCIe 6.0で限界に挑戦:PAM4をPCIeに導入」(PDF)2022年2月16日閲覧。

- ^ 「PowerPointプレゼンテーション」(PDF) . 2022年2月16日閲覧。

- ^ Hachman, Mark (2025年8月1日). 「世界初の最先端PCIe 6.0 SSDが登場(ただし、あなたには不向き)」 . PCWorld . 2025年9月16日閲覧。

- ^ Hachman, Mark (2025年6月11日). 「PCIe 6.0デバイスは2025年の発売に向けて準備万端、次世代接続の到来を告げる」 . PCWorld . 2025年9月16日閲覧。

- ^ a b Hachman, Mark (2025年3月19日). 「PCI Express 7.0の驚異的な速度は間もなく実現するが、PCIe 6はまだ実現していない」 . PCWorld . 2025年7月1日閲覧。

- ^ 「PCI-SIG®、128 GT/sを実現するPCI Express® 7.0仕様を発表」 Business Wire、2022年6月21日。 2022年6月25日閲覧。

- ^ 「PCIe® 7.0仕様、バージョン0.5が利用可能になりました:メンバー向けのフルドラフト版が利用可能」pcisig.com . 2024年4月3日閲覧。

- ^ 「順調に進捗:PCIe 7.0仕様、バージョン0.7が会員レビューに利用可能に」pcisig.com . 2025年1月17日閲覧。

- ^ 「PCIe 7.0仕様、バージョン0.9:最終ドラフトが会員レビューに利用可能に」 pcisig.com . 2025年3月19日閲覧。

- ^ 「PCI-SIG®、128.0 GT/sの転送速度で人工知能の帯域幅需要に対応するPCIe® 7.0仕様をリリース」 Business Wire、2025年6月11日。 2025年6月11日閲覧。

- ^ 「PCI-SIG、2028年までにリリース予定のPCIe 8.0仕様を発表 | PCI-SIG」 pcisig.com . 2025年8月6日閲覧。

- ^ 「PLXデモは、データセンターのクラスタリング相互接続として光ファイバー経由のPCIeを示している」。ケーブル配線工事。Penn Well 。 2012年8月29日閲覧。

- ^ 「光ファイバーシステムで第2世代PCI Express Gen 2を導入」 Adnaco、2011年4月22日。2012年10月4日時点のオリジナルよりアーカイブ。 2012年8月29日閲覧。

- ^ 「PCIeアクティブ光ケーブルシステム」。2014年12月30日時点のオリジナルよりアーカイブ。2015年10月23日閲覧。

- ^ 「IBM Power Systems E870 および E880 の技術概要と紹介」(PDF)。

- ^ 「AcerとAsus、IntelのThunderbolt SpeedテクノロジーをWindows PCに搭載へ」 PC World 2011年9月14日。2012年1月18日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ Kevin Parrish (2013年6月28日). 「PCIe for Mobile 発売; PCIe 3.1、4.0 仕様公開」 . Tom's Hardware . 2014年7月10日閲覧。

- ^ 「PCI Express 4.0 Draft 0.7 & PIPE 4.4仕様 – 設計者にとっての意味とは? — Synopsys技術記事 | ChipEstimate.com」 . www.chipestimate.com . 2018年6月28日閲覧。

- ^ 「PCI Express 1 × 、4×、8×、16×バスのピン配置と配線」。RU :ピン配置。2009年11月25日時点のオリジナルよりアーカイブ。 2009年12月7日閲覧。

- ^ 「PCI ExpressアーキテクチャのPHYインターフェース」(PDF)(バージョン2.00版)。Intel。2008年3月17日時点のオリジナル(PDF)からアーカイブ。 2008年5月21日閲覧。

- ^ 「PCI Express システム アーキテクチャ」(PDF)。

- ^ 「通信」 . Intel .

- ^ 「PCI Expressコネクタの機械図面」 . インターフェースバス. 2007年12月7日閲覧。

- ^ 「PCIeコネクタのFCi回路図」(PDF) FCI connect. 2008年9月20日時点のオリジナル(PDF)からアーカイブ。 2007年12月7日閲覧。

- ^ 「メッセージ シグナル割り込みの使用による割り込み遅延の削減」(PDF)。

- ^ PCI Express 基本仕様、リビジョン 3.0表 4-24

- ^ 「PCIeデータ転送の概要」(PDF)。マイクロチップ・テクノロジー。

- ^ CompTIA A+ Exam Cram (試験問題 220-602, 220-603, 220-604) . ピアソン・エデュケーション. 2007年7月19日. ISBN 978-0-7686-9003-3。

- ^コンピュータ周辺機器とインターフェース技術出版 プネ 2008年ISBN 9788184313086. 2014年2月25日時点のオリジナルよりアーカイブ。2009年7月23日閲覧。

- ^ a b c d e Lawley, Jason (2014年10月28日). 「PCI Expressシステムのパフォーマンスを理解する」(PDF) . 1.2. Xilinx.

- ^ 「NVIDIA、NVIDIA Quadro® Plexを発表 – ビジュアルコンピューティングの飛躍的進歩」。Nvidia 。 2006年8月1日。2006年8月24日時点のオリジナルよりアーカイブ。 2018年7月14日閲覧。

- ^ 「Quadro Plex VCS – 高度な視覚化とリモートグラフィックス」 nVidia。2011年4月28日時点のオリジナルよりアーカイブ。 2010年9月11日閲覧。

- ^ "XGP" . ATI . AMD. 2010年1月29日時点のオリジナルよりアーカイブ。2010年9月11日閲覧。

- ^ Fujitsu-Siemens Amilo GraphicBooster 外付けラップトップGPUがリリースされました、2008年12月3日、2015年10月16日時点のオリジナルよりアーカイブ。 2015年8月9日閲覧。

- ^ AcerのDynaVivid Graphics Dockがフランスに登場、米国ではどうなっているのか?、2010年8月11日、2015年10月16日時点のオリジナルよりアーカイブ。 2015年8月9日閲覧。

- ^ Dougherty, Steve (2010年5月22日)、「MSIがComputexでノートパソコン向け外付けグラフィックソリューション「GUS」を展示」、TweakTown

- ^ Hellstrom, Jerry (2011年8月9日)、「ExpressCardは(それほど)速くないやり方を試みる?」、PC Perspective(社説)、2016年2月1日時点のオリジナルよりアーカイブ。

- ^ 「PE4H V3.2 (PCIe ×16 アダプタ)」 Hwtools.net。2014年2月14日時点のオリジナルよりアーカイブ。2014年2月5日閲覧。

- ^ O'Brien, Kevin (2010年9月8日)、「DIY ViDOCKを使用してノートブックのグラフィックカードをアップグレードする方法」、ノートブックレビュー、2013年12月13日時点のオリジナルよりアーカイブ

- ^ Lal Shimpi, Anand (2011年9月7日)、「Thunderboltデバイスが少しずつ登場:MagmaのExpressBox 3T」、AnandTech 、 2016年3月4日時点のオリジナルよりアーカイブ。

- ^ 「MSI GUS II 外付けGPUエンクロージャ(Thunderbolt搭載)」 The Verge(ハンズオン)2012年1月10日。2012年2月13日時点のオリジナルよりアーカイブ。 2012年2月12日閲覧。

- ^ 「PCI express グラフィックス、Thunderbolt」、Tom's hardware、2012年9月17日

- ^ 「M logics M link Thunderbold chassis no shipping」、Engadget、2012年12月13日、2017年6月25日時点のオリジナルよりアーカイブ。

- ^ Burns, Chris (2017年10月17日)、「2017 Razer Blade Stealth and Core V2 detailed」、SlashGear、2017年10月17日時点のオリジナルよりアーカイブ。

- ^ 「CompactFlash Association、次世代XQDフォーマットの準備を進め、125 MB/秒以上の書き込み速度を約束」 Engadget、2011年12月8日。2014年5月19日時点のオリジナルよりアーカイブ。 2014年5月18日閲覧。

- ^ Zsolt Kerekes (2011年12月). 「Fusion-ioのioDrives / PCIe SSDの設計には何が大きな違いがあるか?」 . storagesearch.com. 2013年9月23日時点のオリジナルよりアーカイブ。 2013年10月2日閲覧。

- ^ 「Fusion-io ioDrive Duo Enterprise PCIe レビュー」 . storagereview.com. 2012年7月16日. 2013年10月4日時点のオリジナルよりアーカイブ。 2013年10月2日閲覧。

- ^ 「OCZ、エンタープライズ向け4 TiB、16 TiBソリッドステートドライブをデモ」 X-bit labs。2013年3月25日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ 「SATA Expressによる高速ストレージアプリケーションの実現」 SATA-IO。2012年11月27日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ 「SATA M.2カード」。SATA-IO。2013年10月3日時点のオリジナルよりアーカイブ。2013年9月14日閲覧。

- ^ 「SCSI Express」 SCSI Trade Association. 2013年1月27日時点のオリジナルよりアーカイブ。 2012年12月27日閲覧。

- ^ Meduri, Vijay (2011年1月24日). 「高性能クラスターインターコネクトとしてのPCI Expressの事例」 HPCwire. 2013年1月14日時点のオリジナルよりアーカイブ。 2012年12月7日閲覧。

- ^ Evan Koblentz (2017年2月3日). 「PCI Express 4.0の延期により次世代の代替技術が強化される可能性」 Tech Republic . 2017年4月1日時点のオリジナルよりアーカイブ。 2017年3月31日閲覧。

- ^ Cutress, Ian. 「CXL仕様1.0リリース:Intelの新しい業界高速インターコネクト」 www.anandtech.com 。 2019年3月11日時点のオリジナルよりアーカイブ。 2019年8月9日閲覧。

- ^ 「Integrators List | PCI-SIG」 . pcisig.com . 2019年3月27日閲覧。

さらに読む

- Budruk, Ravi; Anderson, Don; Shanley, Tom (2003)、Winkles, Joseph 'Joe' (編)、『PCI Express システム アーキテクチャ』、Mind share PC システム アーキテクチャ、Addison-Wesley、ISBN 978-0-321-15630-3、1120ページ。

- Solari, Edward; Congdon, Brad (2003)、『Complete PCI Express Reference: Design Implications for Hardware and Software Developers』、Intel、ISBN 978-0-9717861-9-6、1056ページ。

- Wilen, Adam; Schade, Justin P; Thornburg, Ron (2003年4月)、『PCI Express入門:ハードウェアおよびソフトウェア開発者向けガイド』、Intel、ISBN 978-0-9702846-9-3、325ページ。